# Texas Instruments

# © TVP4020 PERMEDIA 2 Hardware Reference Manual

Issue 6

3Dlabs is the worldwide trading name of 3Dlabs Inc. Ltd. 3Dlabs, GLINT and PERMEDIA are registered trademarks of 3Dlabs.

OpenGL is a trademark of Silicon Graphics, Inc. Windows, Win32, Windows NT, DirectDraw and Direct 3D are trademarks of Microsoft Corp. AutoCAD is a trademark of AutoDesk Inc. MicroStation is a trademark of Bentley Corp.

All other trademarks are acknowledged.

## Contents

| 1. Introduction                          | 1   |

|------------------------------------------|-----|

| 2. Functional Overview                   | 2   |

| 2.1 Block Diagram                        | 2   |

| 2.2 PCI Interface                        |     |

| 2.3 Graphics Core                        | 3   |

| 2.4 Memory Interface                     |     |

| 2.5 Video Timing Generation              |     |

| 2.6 Video Streams                        |     |

| 2.7 Bypass Unit.                         |     |

| 2.8 Reset Configuration Control.         |     |

| 2.9 ROM support<br>2.10 Stereo Support   |     |

| 2.10 Stereo Support                      |     |

| 2.12 TVP4020 VGA Modes                   |     |

| 2.13 PCI Configuration Region            |     |

| 2.14 PCI Register Set                    | 9   |

| 3. Region 0 - Registers                  | 25  |

| 3.1 Region 0 Address Map                 | 25  |

| 3.2 Control Status Registers             |     |

| 3.3 Memory Control Registers             |     |

| 3.4 Video Control Registers              |     |

| 3.5 SVGA Interface                       |     |

| 3.6 RAMDAC Registers                     |     |

| 4. Memory System                         |     |

| 4.1 System Parameters                    |     |

| 4.2 Recommended Parameter Values         |     |

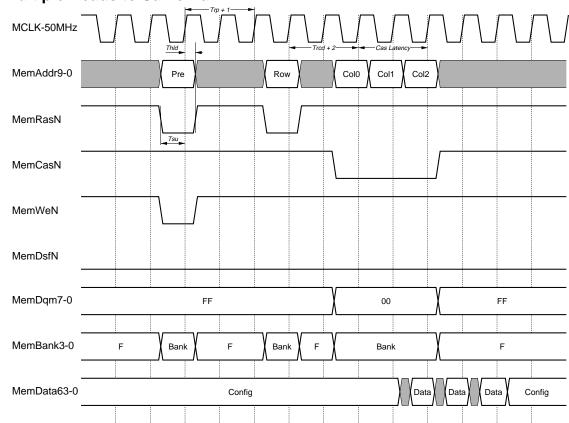

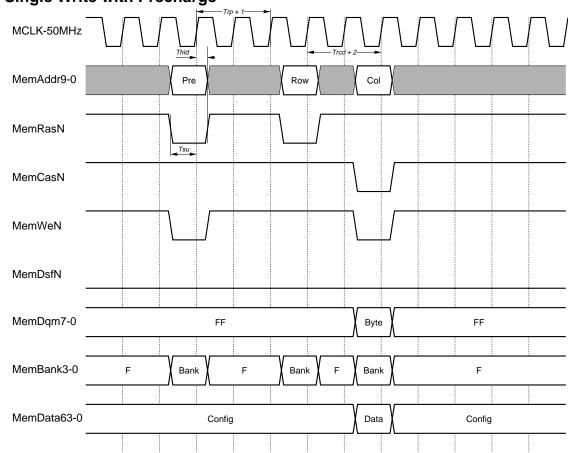

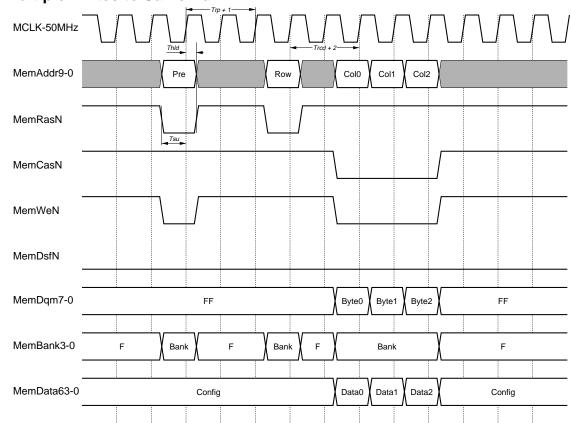

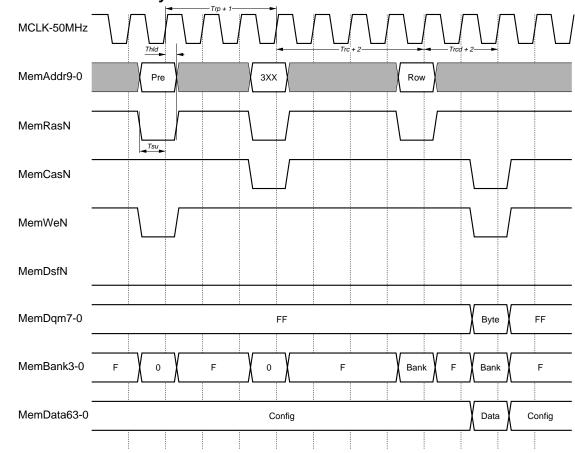

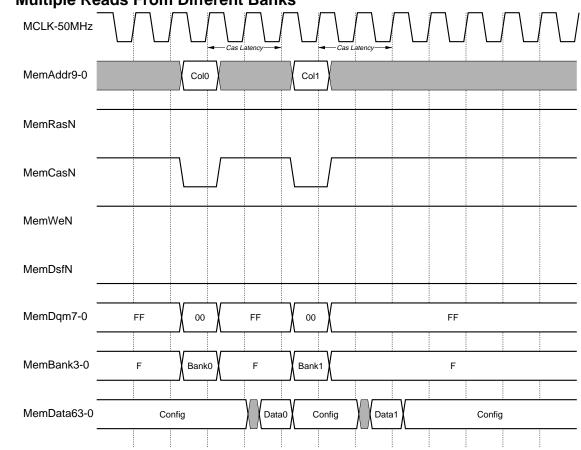

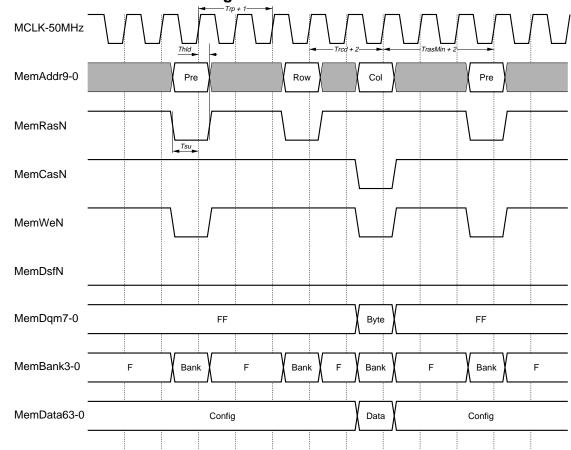

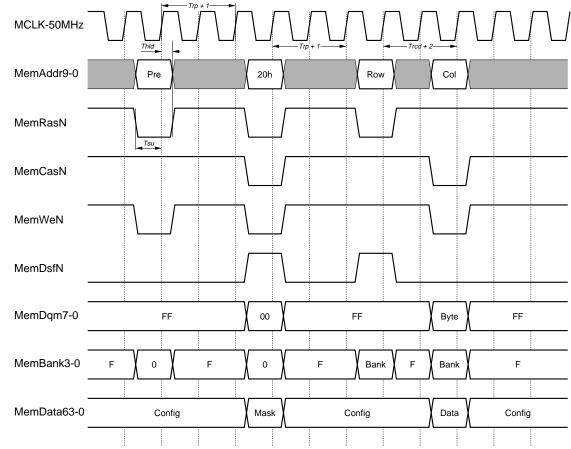

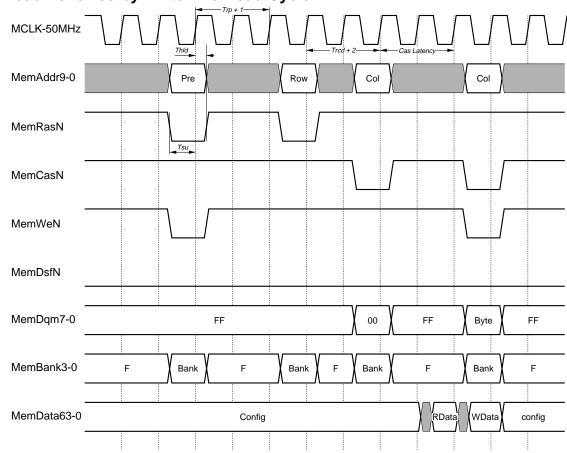

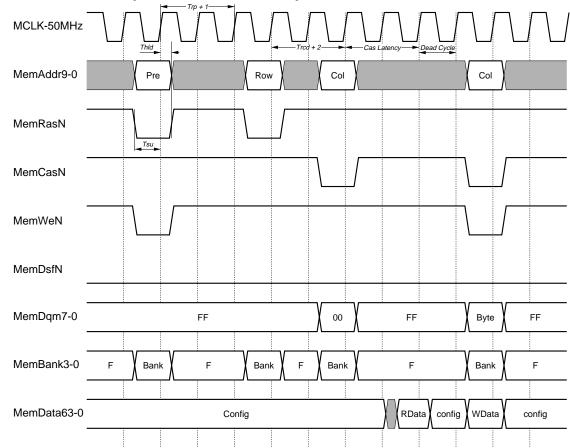

| 4.3 Timing Diagrams                      |     |

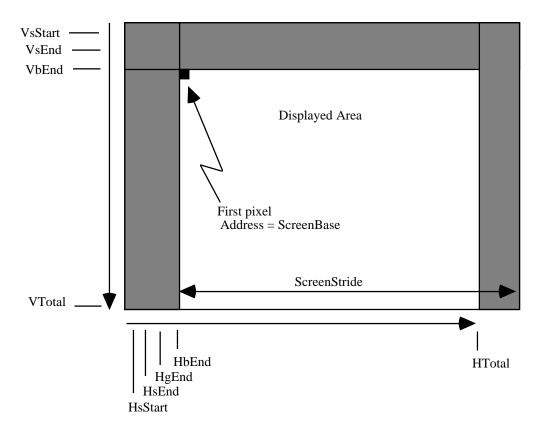

| 5. Video Unit and RAMDAC                 | 115 |

| 5.1 Using the Video Unit                 |     |

| 5.2 Example Timing Values                |     |

| 5.3 Display Data Channel                 |     |

| 5.4 RAMDAC                               |     |

| 5.5 Color Palette RAM                    |     |

| 5.6 Cursor Color Registers               |     |

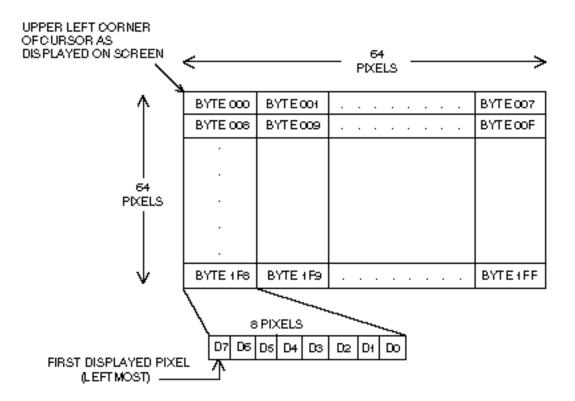

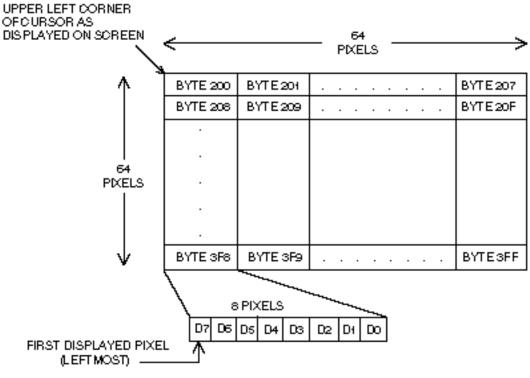

| 5.7 Cursor RAM<br>5.8 Cursor Positioning |     |

| 5.9 PLL Programming                      |     |

| 6. Video Streams Unit                    |     |

|                                          |     |

| 6.1 Stream A                             |     |

| 6.2 Stream B                             |     |

| 6.3 General Purpose Bus<br>6.4 Serial Bus                                                                                                                  | 135        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 6.5 ROM                                                                                                                                                    | 137        |

| 7. Reset Control                                                                                                                                           | 139        |

| 7.1 Reset Control                                                                                                                                          | 139        |

| 8. Electrical Characteristics                                                                                                                              | 140        |

| <ul><li>8.1 Absolute Maximum Ratings</li><li>8.2 DC Specifications</li><li>8.3 AC Specifications</li></ul>                                                 | 140        |

| 9. Pin Assignment                                                                                                                                          | 147        |

| 9.1 Pinlist by Name<br>9.2 Notes to Pin Listing<br>9.3 Pinlist by Number                                                                                   | 154        |

| 10. Package Drawings                                                                                                                                       | 161        |

| 10.1 BGA Side<br>10.2 Overmold Side                                                                                                                        |            |

| 11. Thermal Characteristics                                                                                                                                | 163        |

| <ul> <li>11.1 Device Characteristics</li> <li>11.2 Thermal Model</li> <li>11.3 Operation Without Heatsink</li> <li>11.4 Operation With Heatsink</li> </ul> | 163<br>163 |

| Index                                                                                                                                                      | 165        |

## Figures

| Figure 2.1 TVP4020 Functional Units          | 2   |

|----------------------------------------------|-----|

| Figure 2.1 PCI Configuration Region          | 8   |

| Figure 4.1 Organization of memory devices    | 100 |

| Figure 5.1 Video Timing Parameters           | 115 |

| Figure 5.2 Cursor Plane 0                    | 121 |

| Figure 5.3 Cursor Plane 1                    |     |

| Figure 5.4 Cursor RAM Division Plane 0       |     |

| Figure 5.5 Cursor RAM Division Plane 1       |     |

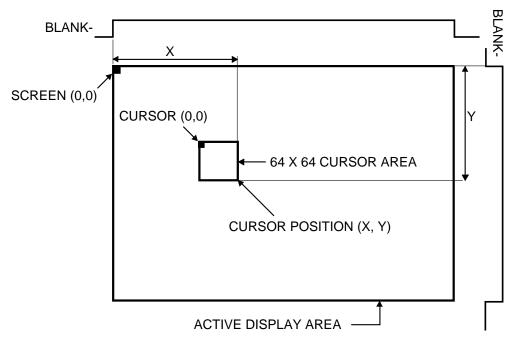

| Figure 5.6 Cursor-Positioning                |     |

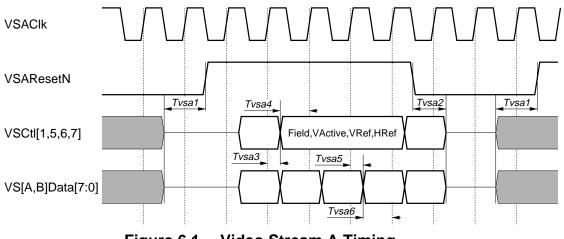

| Figure 6.1 Video Stream A Timing             |     |

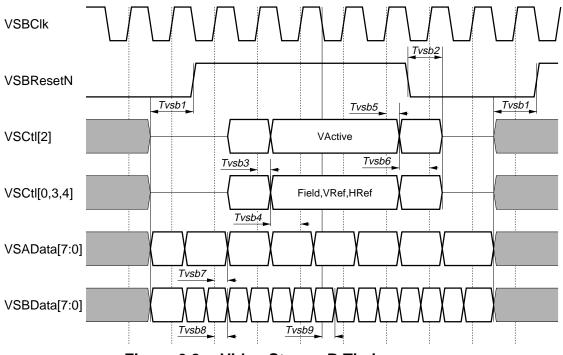

| Figure 6.2 Video Stream B Timing             | 131 |

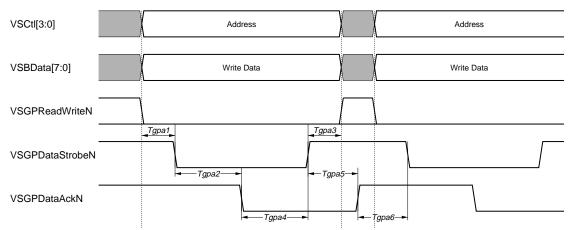

| Figure 6.3 General Purpose Bus Mode A Write  | 134 |

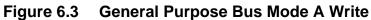

| Figure 6.4 General Purpose Bus Mode A Read   | 134 |

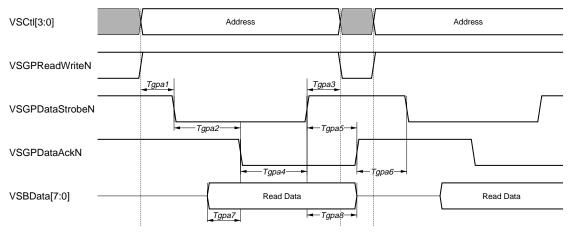

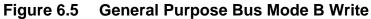

| Figure 6.5 General Purpose Bus Mode B Write  | 134 |

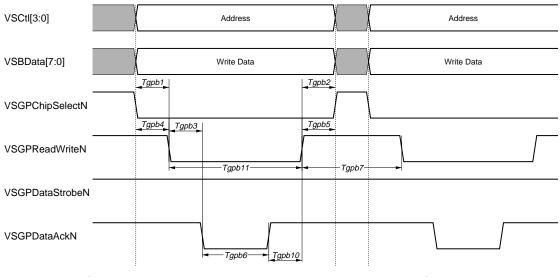

| Figure 6.6 General Purpose Bus Mode B Read   | 135 |

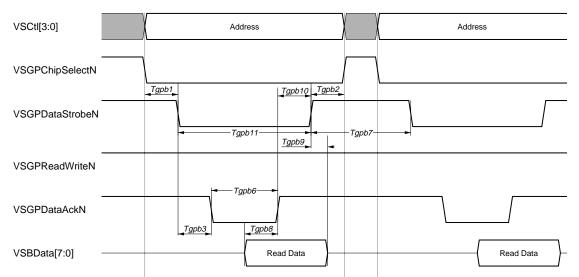

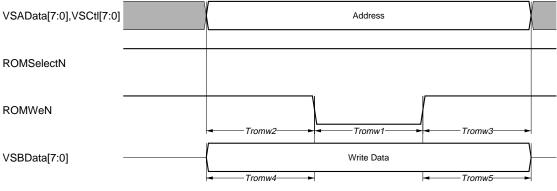

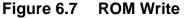

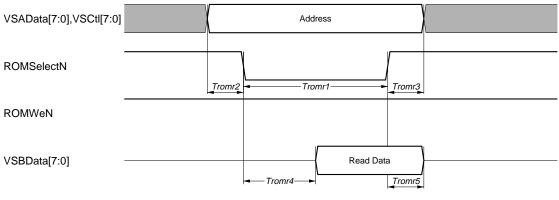

| Figure 6.7 ROM Write                         |     |

| Figure 6.8 ROM Read                          |     |

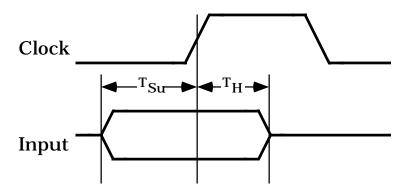

| Figure 8.1 Input Timing Parameters           | 142 |

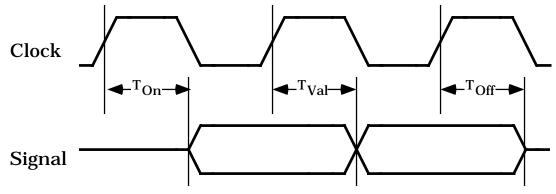

| Figure 8.2 Output Timing Parameters          | 142 |

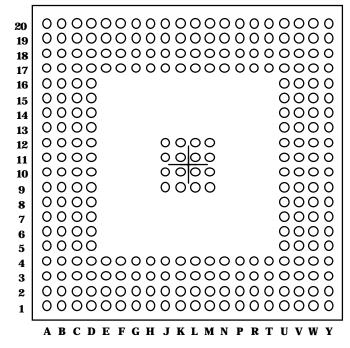

| Figure 9.1 PERMEDIA Pin Numbering (from top) | 147 |

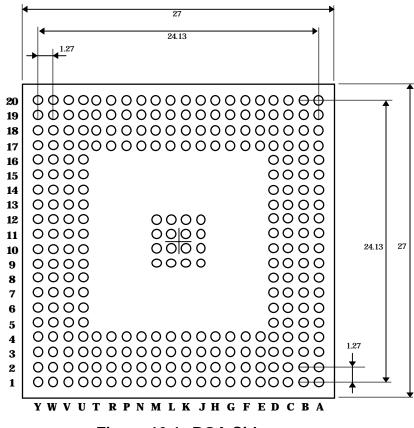

| Figure 10.1 BGA Side                         |     |

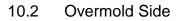

| Figure 10.2 Overmold Side                    | 162 |

## Tables

| Table 2.1 PCI Address Regions                        | 6   |

|------------------------------------------------------|-----|

| Table 2.2 Standard VGA modes                         | 7   |

| Table 2.3 VESA/SVGA modes                            | 7   |

| Table 3.1 Region 0 Address Map                       | 26  |

| Table 4.1 50MHz/Samsung SGRAM (-12)/total SGRAM 4MB. | 103 |

| Table 4.2 66MHz/NEC SGRAM (-12)/total SGRAM 6MB      | 104 |

| Table 4.3 66MHz/NEC SGRAM (-10)/total SGRAM 8MB      |     |

| Table 5.1 Direct Register Map                        | 117 |

| Table 5.2 Indirect Register Map                      |     |

| Table 5.3 Cursor Color Register Address Format       | 120 |

| Table 5.4 Cursor Color Selection Modes               | 120 |

| Table 6.1 Possible Function Combinations             | 126 |

| Table 6.2 Pin Mode Name                              | 127 |

| Table 6.3 Video Stream A Timing                      | 129 |

| Table 6.4 Video Stream B Status                      | 131 |

| Table 6.5 Component Bit Position Formats             | 133 |

| Table 6.6 Mode A and B Pin Sharing                   | 133 |

| Table 6.7 General Purpose Bus Mode Status            | 135 |

| Table 6.8 ROM Write Status                           |     |

| Table 6.9 RO M Read Status                           | 138 |

| Table 9.1 Pinlist by Name                            | 153 |

| Table 9.2 Pinlist by Number                          |     |

| Table 11.1 Operation Without Heatsink                | 163 |

## 1. Introduction

TVP4020 is a high performance PCI/AGP graphics processor that balances high quality 3D polygon and textured graphics acceleration, windows acceleration and state-of-the-art MPEG1/MPEG2 playback with a fast integrated SVGA core, integrated RAMDAC and video ports.

TVP4020 sets the standard for 3D and multimedia acceleration, making it the ideal solution to meet the increasingly pervasive need for balanced 3D and multimedia acceleration - and all in a single, low cost PCI device.

TVP4020 is the second generation PERMEDIA device. Compared with TVP4010, it provides greater flexibility, additional features and enhanced performance. Throughout this manual the terms TVP4020 and PERMEDIA are used interchangeably.

## 2. Functional Overview

#### 2.1 Block Diagram

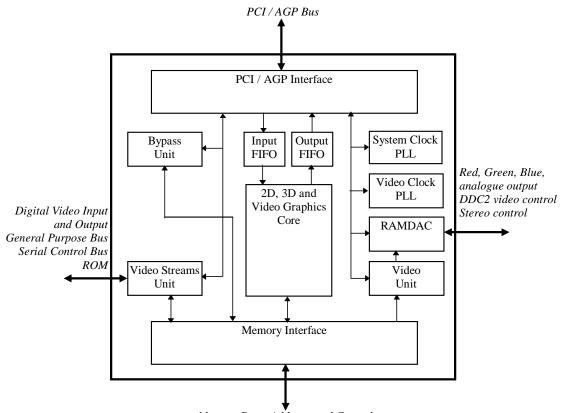

The major TVP4020 functional blocks are shown below:

Memory Data, Address, and Control

Figure 2.1 TVP4020 Functional Units

#### 2.2 PCI Interface

The PCI interface conforms to the PCI Local Bus standard Revision 2.1. TVP4020 is a PCI Local Bus Target, a PCI Local Bus Read Master, and a PCILocal Bus Write Master. It is also an AGP read master with support for pipelined reads and sideband addressing.

The PCI interface has an input FIFO for passing data to the Graphics Core, and an output FIFO for buffering up data to be read from the Graphics Core. The input FIFO is 256 words deep, the output FIFO is 8 words deep. A DMA controller is provided in the PCI interface to allow PERMEDIA to read data directly into the Graphics Core input FIFO or directly out of the output FIFO.

#### 2.3 Graphics Core

The graphics core in PERMEDIA accelerates the key operations for 3D and 2D applications. For further information on the functionality of the graphics core refer to the *TVP4020 Programmer's Reference Manual*.

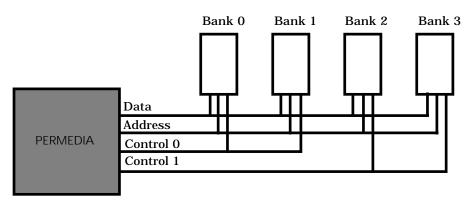

#### 2.4 Memory Interface

The local memory is used to store color, depth, stencil, and texture data. For more information on the different data types and their usage refer to the *TVP4020 Programmer's Reference Manual.*

The memory is organized as 1 to 4 banks of synchronous graphics RAM (SGRAM). Each bank is 64 bits wide and made up of two devices, each 32 bits wide by 256K entries deep. This gives 2Mbytes per bank, with a maximum memory array of 8Mbytes.

Bank zero must always be fitted as the SVGA uses this area for local storage. Any other combination of banks may be fitted, but for contiguous memory banks should be added from 1 to 3.

PERMEDIA will make use of special SGRAM features including block fill and write-per-bit masking. SDRAM may be used in place of SGRAM if it is identical to SGRAM except for missing block write and write per bit masks.

#### 2.5 Video Timing Generation

PERMEDIA has an internal video timing generator and RAMDAC. The RAMDAC has a maximum pixel rate of 230MHz. As all data, including video refreshes, come from the same memory port, the higher video frequencies take away bandwidth that would be used by the graphics processor and reduce performance. Auxiliary Device Support

PERMEDIA can act as a gateway to an additional device which shares address and data lines with the RAMDAC. This device can be mapped into IO space as well as memory space. The auxiliary bus protocol is asynchronous and supports a wait signal that the slave device may use to insert wait states into a transaction.

#### 2.6 Video Streams

PERMEDIA has support for the input and output of digital video. Both these video streams are independent of each other and the video from the RAMDAC. Input video may be used as a texture map for special video effects. Output video is designed to drive TV encoder chips.

Vertical blanking interval data may be separated from the input stream or inserted into the output stream as required.

#### 2.7 Bypass Unit

The bypass unit allows direct access of the memory from the PCI bus. It includes data formatting and a read master DMA controller which is optimized for texture loading.

#### 2.8 Reset Configuration Control

A minimal number of parameters may be configured at reset by resistors attached to the Video Streams data port. Other configuration information should be loaded from a ROM or configuration file following reset. See the Reset Control section for more details.

The PCI Sub-System ID and Sub-System Vendor ID may be loaded directly from the ROM immediately after reset. The information is loaded from the highest address in the ROM.

If a ROM is not fitted these registers are made write-once so that the BIOS or driver software may load them as required.

#### 2.9 ROM support

PERMEDIA supports a Flash ROM. This ROM may store code needed for devicespecific initialization and the SVGA BIOS.

#### 2.10 Stereo Support

Stereo functionality on PERMEDIA is controlled via the VideoControl and ScreenBaseRight registers.

The StereoEnable bit in the VideoControl register is used to enable and disable the stereo functionality. When the StereoEnable bit is set to 1, alternate frames are displayed from different framebuffer locations and the VidRightEye pin will indicate which frame is being displayed.

If the RightEyeCtl bit in the VideoControl register is set to 0, then Active High on the VidRightEye pin will indicate that the "Right" frame is being displayed. If the RightEyeCtl bit is set to 1, then Active Low on the VidRightEye pin will indicate that the "Right" frame is being displayed.

The RightFrame bit in the VideoControl register is a read only register which also indicates which frame is being displayed: 0 indicates "Left" frame, 1 indicates "Right" frame.

The ScreenBaseRight register should be loaded with the base address in the framebuffer of the "Right" frame. The base address in the framebuffer of the "Left" frame is given by the standard ScreenBase address.

#### 2.11 Address Map

PERMEDIA has six PCI base address regions:

| Region        | Description              |

|---------------|--------------------------|

| Configuration | PCI configuration region |

| 0             | GC control region        |

| 1             | Bypass access to memory  |

| 2             | Bypass access to memory  |

| ROM           | Expansion ROM            |

| SVGA          | SVGA Addresses           |

#### Table 2.1PCI Address Regions

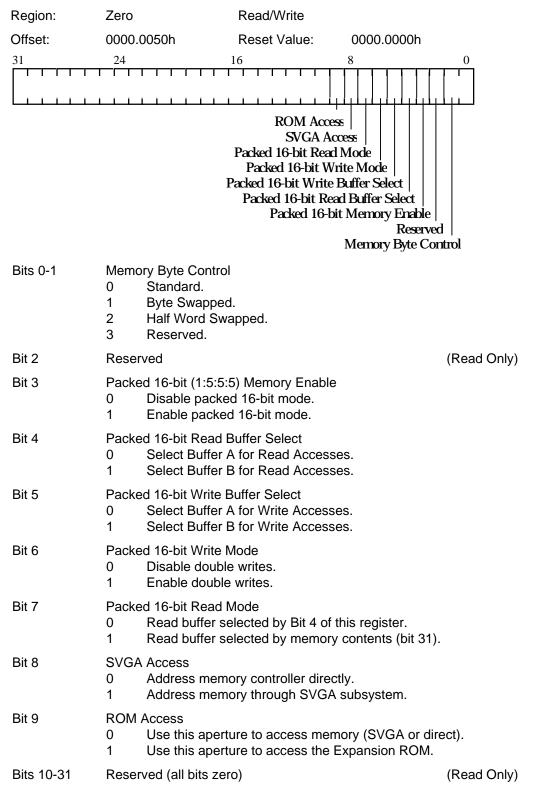

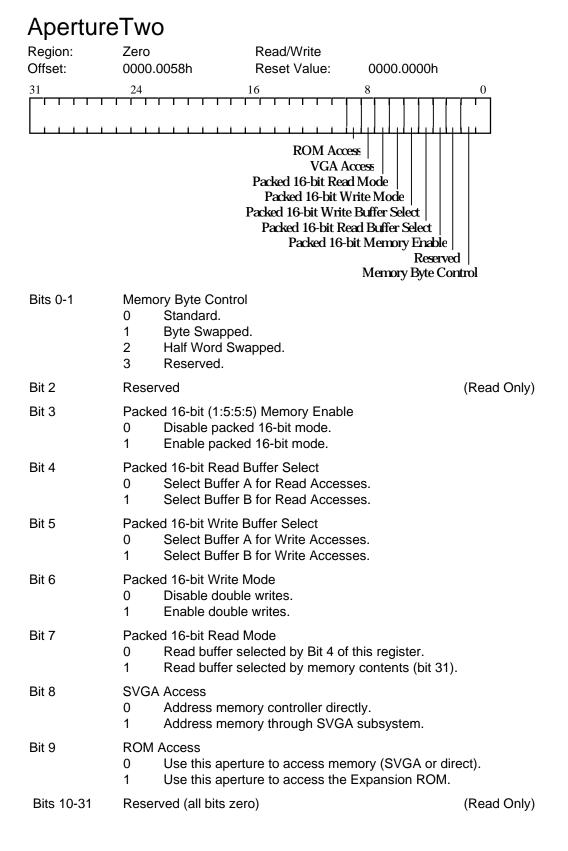

Two memory apertures are provided, each is a PCI region with a fixed size of 8 MBytes. A variety of access modes are available, including byte swapped, halfword swapped, and packed 16-bit pixel modes to support per-window double buffering with a suitable RAMDAC. Each aperture can be programmed to address the memory controller directly, or to address the memory through the VGA subsystem. The two separately controlled apertures allow different views of the memory to co-exist without register re-programming; for example, one aperture could be set for localbuffer data accesses and the other for framebuffer data accesses.

The two memory apertures can also be programmed to allow reading and writing of the ROM instead of memory. This ensures that the ROM is visible beyond system boot time, making it possible to program a Flash ROM device in situ.

When displaying images in 16-bit per-window double buffered mode the framebuffer area of memory is divided into two interleaved buffers, A and B. Each pixel uses 32 bits: the bottom 16 bits (15:0) form buffer A, and the top 16 bits (31:16) form buffer B. The top bit in Buffer B is used by the RAMDAC to select which buffer is displayed, on a per-pixel basis.

The control registers for each of Memory Apertures One and Two can be set to allow reading and writing of buffers A and B as contiguous 16-bit packed buffers although they are pixel interleaved in the memory. Each 32-bit read or write access over the PCI bus thus transfers two pixels to/from the selected 16-bit packed buffer. The apertures can be programmed to access either buffer A or buffer B, to write to both buffer A and buffer B, or to read from the active buffer as specified by bit 31.

A further control bit is provided to route the memory address via the SVGA controller, rather than directly to the main memory controller. This allows the memory address to be interpreted as a SVGA address. This mechanism allows the SVGA to be relocated away from the standard fixed addresses. The fixed addresses may be optionally disabled so that two SVGA systems can co-exist on the same bus.

#### 2.12 TVP4020 VGA Modes

|           | The following standard VOV modes are supported. |                 |           |            |             |                |            |

|-----------|-------------------------------------------------|-----------------|-----------|------------|-------------|----------------|------------|

| Mo<br>(he |                                                 | Alpha<br>Format | Char Size | Colors     | Max<br>Page | Type<br>Format | Resolution |

| 00        |                                                 | 40 by 25        | 8 by 8    | 16/256K bw | 8           | Alpha          | 320 by 200 |

|           | 0*                                              | 40 by 25        | 8 by 14   | 16/256K bw | 8           | Alpha          | 320 by 350 |

|           | 0+                                              | 40 by 25        | 9 by 16   | 16/256K bw | 8           | Alpha          | 360 by 400 |

| 01        | 1                                               | 40 by 25        | 8 by 8    | 16/256K    | 8           | Alpha          | 320 by 200 |

| _         | 1*                                              | 40 by 25        | 8 by 14   | 16/256K    | 8           | Alpha          | 320 by 350 |

|           | 1+                                              | 40 by 25        | 9 by 16   | 16/256K    | 8           | Alpha          | 360 by 400 |

| 02        | 2                                               | 80 by 25        | 8 by 8    | 16/256K bw | 8           | Alpha          | 640 by 200 |

|           | 2*                                              | 80 by 25        | 8 by 14   | 16/256K bw | 8           | Alpha          | 640 by 350 |

|           | 2+                                              | 80 by 25        | 9 by 16   | 16/256K bw | 8           | Alpha          | 720 by 400 |

| 03        | 3                                               | 80 by 25        | 8 by 8    | 16/256K    | 8           | Alpha          | 720 by 200 |

|           | 3*                                              | 80 by 25        | 8 by 14   | 16/256K    | 8           | Alpha          | 640 by 350 |

|           | 3+                                              | 80 by 25        | 9 by 16   | 16/256K    | 8           | Alpha          | 720 by 400 |

| 04        | 4                                               | 40 by 25        | 8 by 8    | 4/256K     | 1           | Graph          | 320 by 200 |

| 05        | 5                                               | 40 by 25        | 8 by 8    | 4/256K bw  | 1           | Graph          | 320 by 200 |

| 06        | 6                                               | 80 by 25        | 8 by 8    | 2/256K bw  | 1           | Graph          | 640 by 200 |

| 07        | 7                                               | 80 by 25        | 9 by 14   | bw         | 8           | Alpha          | 720 by 350 |

|           | 7+                                              | 80 by 25        | 9 by 16   | bw         | 8           | Alpha          | 720 by 400 |

| 0D        | D                                               | 40 by 25        | 8 by 8    | 16/256K    | 8           | Graph          | 320 by 200 |

| 0E        | Е                                               | 80 by 25        | 8 by 8    | 16/256K    | 4           | Graph          | 640 by 200 |

| 0F        | F                                               | 80 by 25        | 8 by 14   | bw         | 2           | Graph          | 640 by 350 |

| 10        | 10                                              | 80 by 25        | 8 by 14   | 16/256K    | 2           | Graph          | 640 by 350 |

| 11        | 11                                              | 80 by 30        | 8 by 16   | 2/256K     | 1           | Graph          | 640 by 480 |

| 12        | 12                                              | 80 by 30        | 8 by 16   | 16/256K    | 1           | Graph          | 640 by 480 |

| 13        | 13                                              | 40 by 25        | 8 by 8    | 256/256K   | 1           | Graph          | 320 by 200 |

The following standard VGA modes are supported:

#### Table 2.2Standard VGA modes

The following VESA SVGA modes are supported:

| Mode (he | ex) Pix | els    | Colors |

|----------|---------|--------|--------|

| 100      | 640     | by 400 | 256    |

| 101      | 640     | by 480 | 256    |

Table 2.3 VESA/SVGA modes

ModeX is also supported.

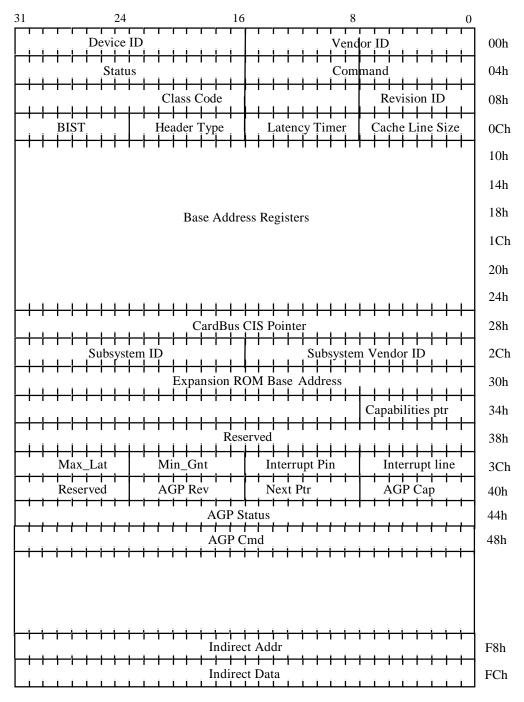

#### 2.13 PCI Configuration Region

The PCI Configuration Region provides information which satisfies the needs of current and anticipated system configuration mechanisms.

Figure 2.1 PCI Configuration Region

#### 2.14 PCI Register Set

For more information about the use of the registers in this section refer to the PCI Specification.

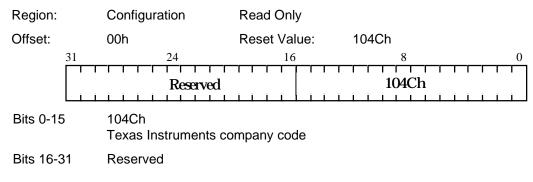

#### 2.14.1 Vendor ID

Vendor identification number.

## CFGVendorld

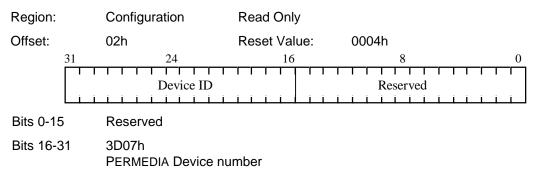

#### 2.14.2 Device ID

Device identification number.

## CFGDeviceId

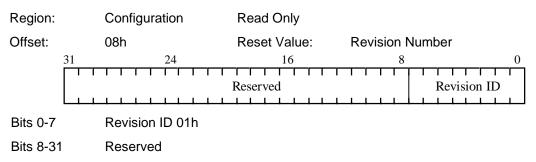

#### 2.14.3 Revision ID

Revision identification number.

## CFGRevisionId

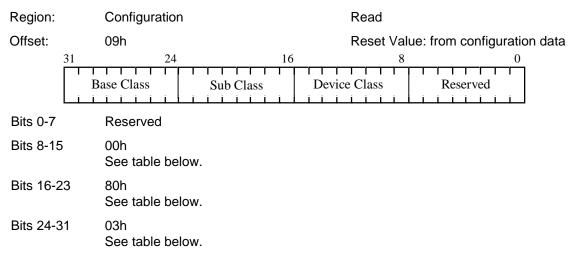

#### 2.14.4 Class Code Register

This register is used to identify the generic function of PERMEDIA, which depends on the setting of configuration data detailed below.

## CFGClassCode

| BaseClassZer      | Fixed VGA<br>Addressin | Bass<br>Clas | Sub<br>Class | Inter<br>face | Meaning                    |

|-------------------|------------------------|--------------|--------------|---------------|----------------------------|

| o<br>(config bit) | g                      | S            | Class        | lace          | (see PCI Spec Appendix D)  |

| 0                 | Disabled               | 03h          | 80h          | 00h           | "Other" display controller |

| 0                 | Enabled                | 03h          | 01h          | 00h           | VGA-compatible controller  |

| 1                 | Disabled               | 00h          | 00h          | 00h           | Non VGA-compatible device  |

| 1                 | Enabled                | 00h          | 01h          | 00h           | VGA-compatible device      |

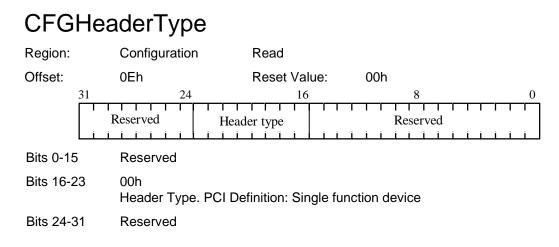

#### 2.14.5 Header Type

#### 2.14.6 Command Register

The command register provides control over a device's ability to generate and respond to PCI cycles. Writing zero to this register disconnects the device from the PCI for all except configuration accesses. PERMEDIA 2 supports all necessary bits within the command register for the functionality it contains.

## CFGCommand

| Region:    | Configuration                                                                              | Read/Write                              |                                            |

|------------|--------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------|

| Offset:    | 04h                                                                                        | Reset Value:                            | 00h                                        |

|            | 24<br>Reserved                                                                             |                                         | 8 0<br>Command                             |

| Bit 0      | I/O Space Enable<br>0 = Disable I/O space<br>1 = Enable I/O space<br>If fixed SVGA addres  | accesses.                               | s bit will be 0 (read-only).               |

| Bit 1      | Memory Space Enab<br>0 = Disable memory s<br>1 = Enable memory s                           | space accesses.                         |                                            |

| Bit 2      | Bus Master Enable<br>0 = Disable master a<br>1 = Enable master ac                          |                                         |                                            |

| Bit 3      | Special Cycle Enable<br>0 = PERMEDIA neve                                                  |                                         | (Read Only)<br>ial cycle accesses.         |

| Bit 4      | Memory Write and In<br>0 = "Memory Write ar                                                |                                         | (Read Only)<br>ver generated.              |

| Bit 5      | SVGA Palette Snoop<br>0 = Treat palette acco<br>1 = Enable SVGA pa<br>If fixed SVGA addres | esses like all other<br>lette snooping. |                                            |

| Bit 6      | Parity Error Respons<br>0 = PERMEDIA does                                                  |                                         | (Read Only) error reporting.               |

| Bit 7      | Address/Data steppir<br>0 = PERMEDIA does                                                  | -                                       | (Read Only)<br>ng.                         |

| Bit 8      | SERR driver enable<br>0 = PERMEDIA does                                                    | not support parity                      | (Read Only)<br>error reporting.            |

| Bit 9      | Master Fast Back-to-<br>0 = The PERMEDIA                                                   |                                         | (Read Only)<br>fast back-to-back accesses. |

| Bits 10-15 | Reserved<br>00.0000b.                                                                      |                                         | (Read Only)                                |

| Bits 16-31 | Reserved.                                                                                  |                                         |                                            |

### 2.14.7 Status Register

## **CFGStatus**

| Region:   | Configuration                                                                                        | Read                                       |                     |                                                       |

|-----------|------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------|-------------------------------------------------------|

| Offset:   | 06h                                                                                                  | Reset Value:                               | 00h                 |                                                       |

|           | 24<br>Reserved                                                                                       |                                            | 8<br>Status         |                                                       |

| Bits 0-4  | Reserved<br>0.0000b.                                                                                 |                                            |                     | (Read Only)                                           |

| Bit 5     | 66 MHz Capable<br>0 = PERMEDIA is 33                                                                 | MHz capable only.                          |                     | (Read Only)                                           |

| Bit 6     | UDF Supported<br>0 = PERMEDIA does                                                                   | not support user-de                        | efinable configura  | (Read Only)<br>ations.                                |

| Bit 7     | Fast Back-to-Back Ca<br>1 = PERMEDIA can a                                                           |                                            | back PCI transad    | (Read Only)<br>ctions.                                |

| Bit 8     | Data Parity Error Det<br>0 = Parity checking n                                                       |                                            | PERMEDIA .          | (Read Only)                                           |

| Bits 9-10 | DEVSEL Timing<br>01b = PERMEDIA as                                                                   | serts DEVSEL# at r                         | medium speed.       | (Read Only)                                           |

| Bit 11    | Signaled Target Abor<br>0 = PERMEDIA neve                                                            |                                            | ort.                | (Read Only)                                           |

| Bit 12    | Received Target Abo<br>This bit is set by the I<br>terminated with Targe                             | PERMEDIA bus ma                            | ster whenever its   | s transaction is                                      |

| Bit 13    | Received Master Abo<br>This bit is set by the I<br>terminated with Mast                              | PERMEDIA bus ma                            | ster whenever its   | s transaction is                                      |

| Bit 14    | Signaled System Erro<br>0 = PERMEDIA neve                                                            |                                            | error.              | (Read Only)                                           |

| Bit 15    | Detected Parity Error<br>0 = Parity checking is<br>Writes to this register<br>the register is loaded | s not implemented b<br>cause bits to be re | set, but not set. / | (Read Only)<br>A bit is reset whenever<br>set to one. |

| Bit 16-31 | Reserved                                                                                             |                                            |                     |                                                       |

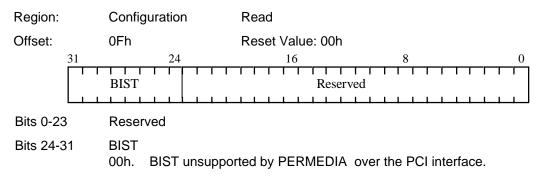

#### 2.14.8 BIST

Optional register used for control and status of BIST.

## **CFGBist**

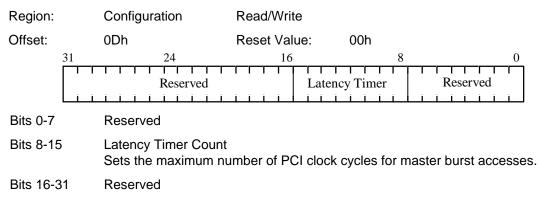

#### 2.14.9 Latency Timer

This register specifies, in PCI bus clocks, the value of the Latency Timer for this PCI bus master.

## CFGLatTimer

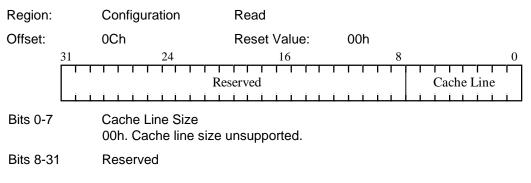

#### 2.14.10 Cache Line Size

This register specifies the cache line size in units of 32 bit words. It is only implemented for masters which use the 'Memory write and invalidate' command. PERMEDIA 2 does not use this command.

## CFGCacheLine

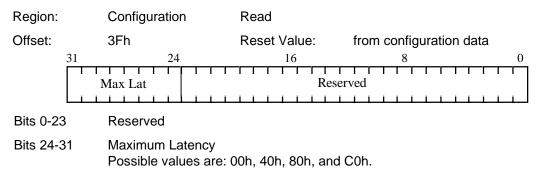

#### 2.14.11 Maximum Latency

This register specifies how often the PCI device needs to gain access to the PCI bus.

## CFGMaxLat

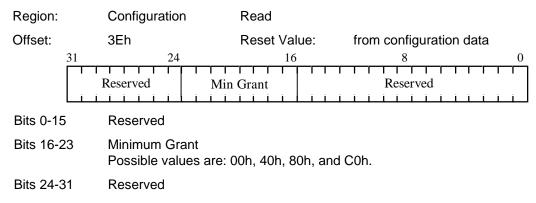

#### 2.14.12 Minimum Grant

This register specifies how long a burst period the PCI device needs.

## CFGMinGrant

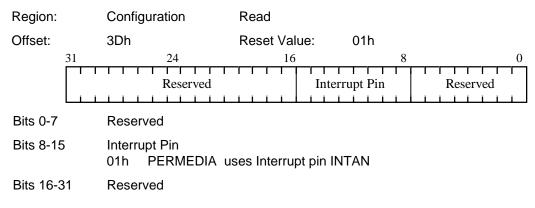

#### 2.14.13 Interrupt Pin

The Interrupt Pin register specifies which line PERMEDIA uses.

## **CFGIntPin**

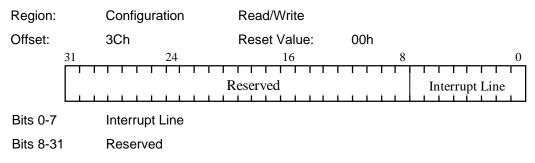

#### 2.14.14 Interrupt Line

The Interrupt Line register in an 8-bit register used to communicate interrupt line routing information.

## CFGIntLine

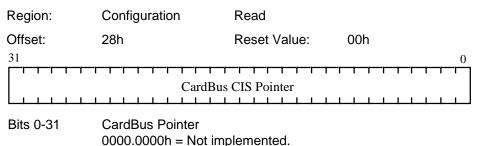

#### 2.14.15 CardBus CIS Pointer

## CFGCardBus

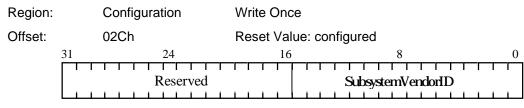

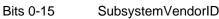

2.14.16 Subsystem Vendor ID

This register is used to identify the vendor of the add-in board on which the PERMEDIA device resides. It has two possible reset states: the value may be loaded from the ROM byte addresses FFFCh and FFFDh, or reset to the Vendor ID and then written to once before it becomes read only. The option is controlled by a configuration resistor.

## **CFGSubsystemVendorId**

Bits 16-31 Reserved

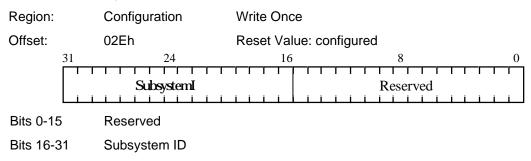

#### 2.14.17 Subsystem ID

This register is used to identify the add-in board on which the PERMEDIA device resides. It has two possible reset states: the value may be loaded from the ROM byte addresses FFFEh and FFFFh, or reset to the Device ID and then written to once before it becomes read only. The option is controlled by a configuration resistor.

## CFGSubsystemId

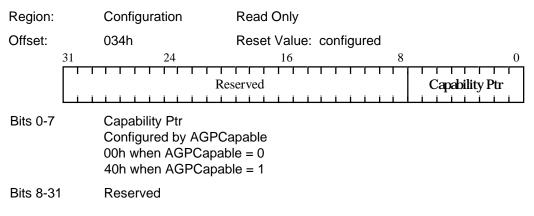

#### 2.14.18 Capabilities Pointer

The Capabilities Pointer register is an eight bit register used to provide an offset into the configuration space for the first item a capabilities list. In an AGP system, it is used to point to the AGP capability registers.

## CFGCapPtr

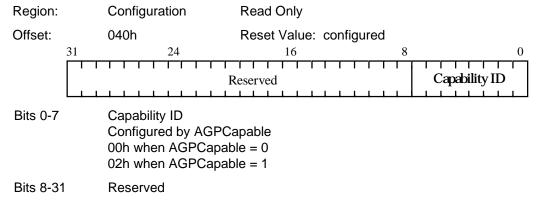

#### 2.14.19 Capability ID

This register specifies that the device has AGP capability.

## CFGCapID

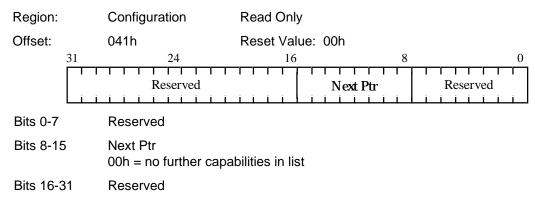

#### 2.14.20 Next Pointer

This register points to the next capability data structure. However as there are no more, it is set to zero.

## CFGNextPtr

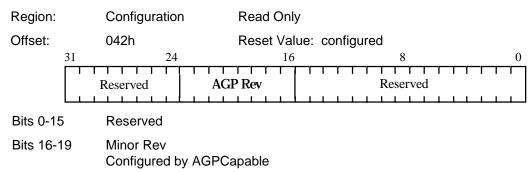

#### 2.14.21 AGP Revision

This register reports the revision of the AGP specification that the device conforms to.

## CFGAGPRev

| 0h when AGPCapable = 0 |  |

|------------------------|--|

| 0h when AGPCapable = 1 |  |

| Bits 20-23 | Major Rev<br>Configured by AGPCapable<br>0h when AGPCapable = 0<br>1h when AGPCapable = 1 |

|------------|-------------------------------------------------------------------------------------------|

| Bits 24-31 | Reserved                                                                                  |

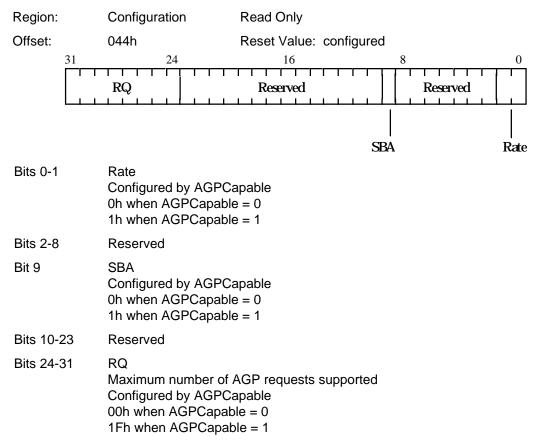

#### 2.14.22 AGP Status

This register describes the AGP capabilities of the device.

## **CFGAGPStatus**

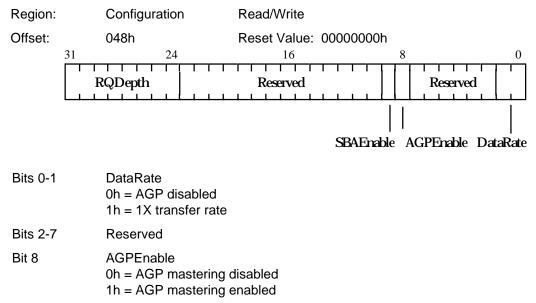

#### 2.14.23 AGP Command

This register controls the operation of the AGP interface.

## CFGAGPCommand

- Bit 9 SBAEnable 0h = sideband addressing disabled 1h = sideband addressing enabled

- Bits 10-23 Reserved

- Bits 24-31 RQDepth Maximum number of AGP requests which can be queued.

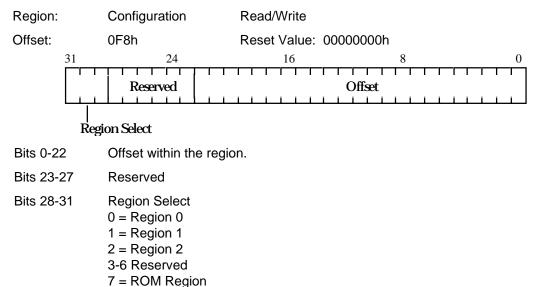

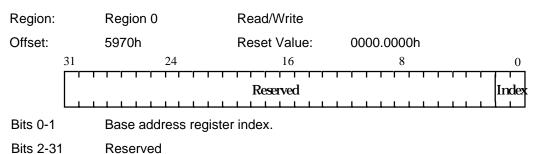

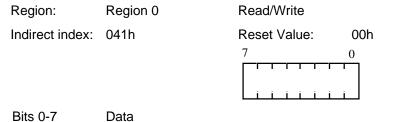

#### 2.14.24 Indirect Address

This register and the Indirect Data register are used to access regions 0, 1, and 2, and the ROM region indirectly. The region and offset to be accessed are loaded into the Indirect Address register and the Indirect Data register read from or written to as appropriate.

## CFGIndirectAddress

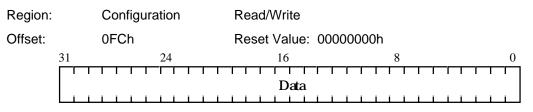

#### 2.14.25 Indirect Data

This register and the Indirect Address register are used to access regions 0, 1, and 2, and the ROM region indirectly. The region and offset to be accessed are loaded into the Indirect Address register and the Indirect Data register read from or written to as appropriate.

## **CFGIndirectData**

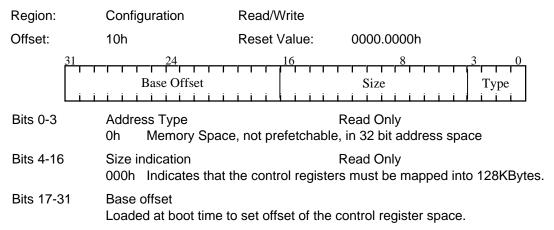

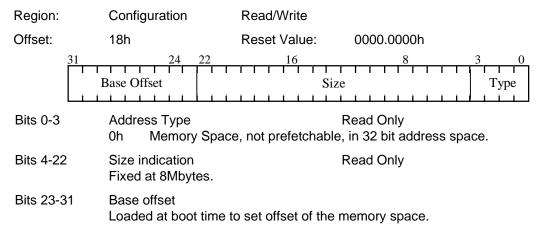

#### 2.14.26 Base Address 0 Register

The Base Address 0 Register contains the PERMEDIA 2 control space offset. The control registers are in memory space. They are not prefetchable and can be located anywhere in 32 bit address space.

## CFGBaseAddr0

#### 2.14.27 Base Address 1 Register

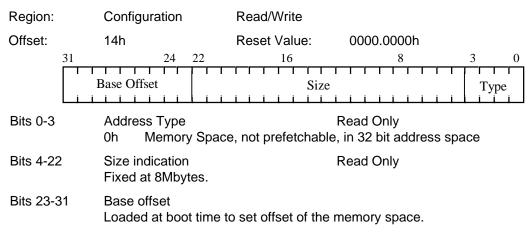

The Base Address 1 Register contains the PERMEDIA aperture one memory offset. It is not prefetchable and can be located anywhere in 32 bit address space.

## CFGBaseAddr1

#### 2.14.28 Base Address 2 Register

The Base Address 2 register contains PERMEDIA aperture two memory offset. It is not prefetchable and can be located anywhere in 32 bit address space.

## CFGBaseAddr2

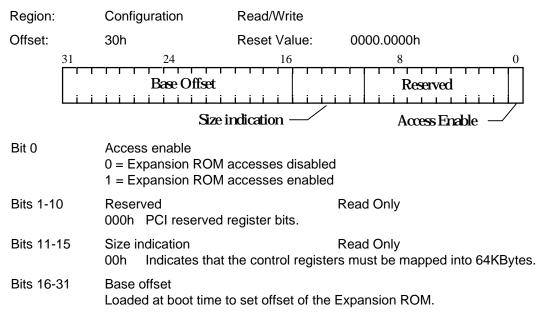

#### 2.14.29 Expansion ROM Base Address

The Expansion ROM Base register is the offset address for the expansion ROM.

## CFGRomAddr

## 3. Region 0 - Registers

#### 3.1 Region 0 Address Map

The PERMEDIA Region Zero is a 128Kbyte region containing the control registers, and ports to and from the graphics processor. The control space is mapped in twice within the 128KByte region. In the second 64K the registers are mapped to be byte swapped for big endian hosts.

| Address Range             | Region Select           | Byte Swap |

|---------------------------|-------------------------|-----------|

| 0000.0000 -><br>0000.1FFF | Control Status          | No        |

| 0000.1000 -><br>0000.1FFF | Memory Control          | No        |

| 0000.2000 -><br>0000.2FFF | GP FIFO Access          | No        |

| 0000.3000 -><br>0000.3FFF | Video Control           | No        |

| 0000.4000 -><br>0000.4FFF | RAMDAC                  | No        |

| 0000.5000 -><br>0000.57FF | Video Stream GP<br>Bus  | No        |

| 0000.5800 -><br>0000.5FFF | Video Stream<br>Control | No        |

| 0000.6000 -><br>0000.6FFF | VGA Control             | No        |

| 0000.7000 -><br>0000.7FFF | Reserved                | No        |

| 0000.8000 -><br>0000.FFFF | GP Registers            | No        |

| 0001.0000 -><br>0001.1FFF | Control Status          | Yes       |

| 0001.1000 -><br>0001.1FFF | Memory Control          | Yes       |

| 0001.2000 -><br>0001.2FFF | GP FIFO Access          | Yes       |

| 0001.3000 -><br>0001.3FFF | Video Control           | Yes       |

| 0001.4000 -><br>0001.4FFF | RAMDAC                  | Yes       |

| 0001.5000 -><br>0001.57FF | Video Stream GP<br>Bus  | Yes       |

| 0001.5800 -><br>0001.5FFF | Video Stream<br>Control | Yes       |

| 0001.6000 -><br>0001.6FFF | VGA Control             | Yes       |

| 0001.7000 -><br>0001.7FFF | Reserved                | Yes       |

| 0001.8000 -><br>0001.FFFF | GP Registers            | Yes       |

### Table 3.1Region 0 Address Map

#### 3.2 **Control Status Registers**

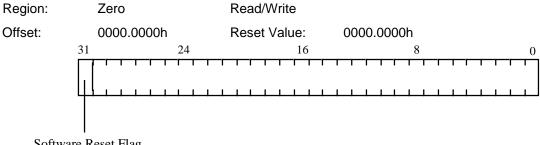

#### 3.2.1 **Reset Status Register**

Writing to the reset status register forces a software reset of the PERMEDIA Graphics Processor. The software reset does not reset the PCI interface but is otherwise the same as a hardware reset.

The software reset takes a number of cycles and the Graphics Processor must not be used during the reset. A flag in the register is provided which shows that the software reset is still in progress.

## **ResetStatus**

Software Reset Flag

- Bits 0-30 Reserved Bit 31 Software reset flag The GC is ready for use 0 1

- The GC is being reset and must not be used

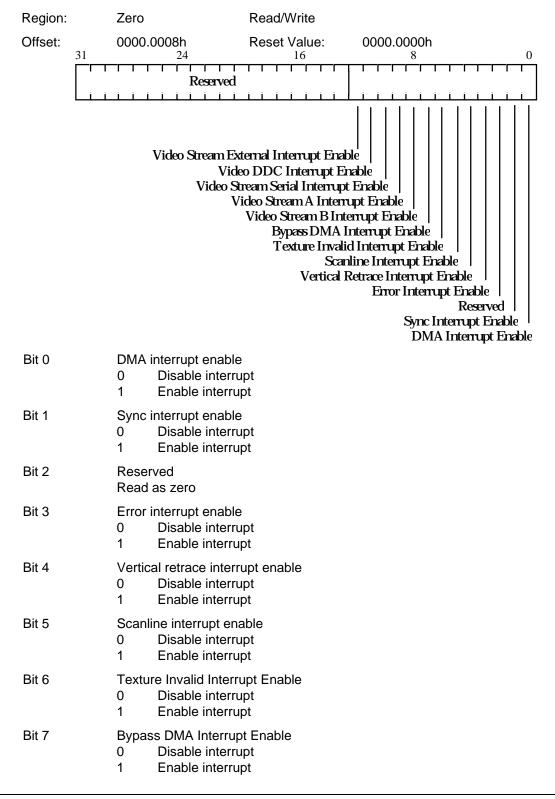

#### 3.2.2 Interrupt Enable Register

The Interrupt Enable Register allows for a number of PERMEDIA flags to generate a PCI interrupt. At reset all interrupts sources are disabled.

## IntEnable

| Bit 8      | Video Stream B Interrupt Enable<br>0 Disable interrupt<br>1 Enable interrupt                                    |

|------------|-----------------------------------------------------------------------------------------------------------------|

| Bit 9      | Video Stream A Interrupt Enable<br>0 Disable interrupt<br>1 Enable interrupt                                    |

| Bit 10     | Video Stream Serial Interrupt Enable0Disable interrupt1Enable interrupt                                         |

| Bit 11     | <ul><li>Video DDC Interrupt Enable</li><li>0 Disable interrupt</li><li>1 Enable interrupt</li></ul>             |

| Bit 12     | <ul><li>Video Stream External Interrupt Enable</li><li>0 Disable interrupt</li><li>1 Enable interrupt</li></ul> |

| Bits 13-31 | Reserved<br>Read as zero                                                                                        |

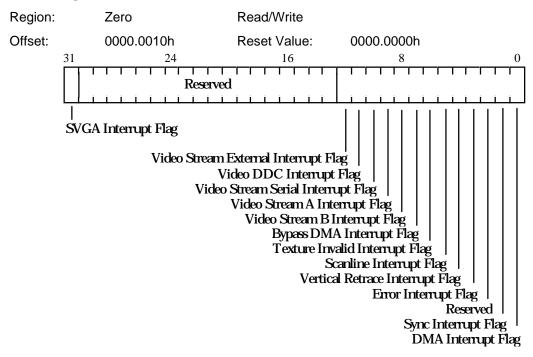

#### 3.2.3 Interrupt Flags

The Interrupt Flags Register shows which interrupts are outstanding. Flag bits are reset by writing to this register with the corresponding bit set to a one. Flags at positions where the bits are set to zero will be unaffected by the write. (The exception is bit 31, which is read-only and reflects the state of the interrupt line from the SVGA Unit. The SVGA Interrupt must be enabled and reset by accessing the SVGA Unit directly, but is visible in this register for convenience.)

## IntFlags

| Bit 0      | <ul><li>DMA interrupt Flag</li><li>0 No interrupt</li><li>1 Interrupt outstanding</li></ul> |

|------------|---------------------------------------------------------------------------------------------|

| Bit 1      | Sync interrupt flag<br>0 No interrupt<br>1 Interrupt outstanding                            |

| Bit 2      | Reserved<br>Read as zero                                                                    |

| Bit 3      | Error interrupt flag<br>0 No interrupt<br>1 Interrupt outstanding                           |

| Bit 4      | Vertical retrace interrupt flag<br>0 No interrupt<br>1 Interrupt outstanding                |

| Bit 5      | Scanline interrupt flag<br>0 No interrupt<br>1 Interrupt outstanding                        |

| Bit 6      | Texture Invalid Interrupt flag0No interrupt1Interrupt outstanding                           |

| Bit 7      | Bypass DMA Interrupt Flag<br>0 No interrupt<br>1 Interrupt outstanding                      |

| Bit 8      | Video Stream B Interrupt flag<br>0 No interrupt<br>1 Interrupt outstanding                  |

| Bit 9      | Video Stream A Interrupt flag<br>0 No interrupt<br>1 Interrupt outstanding                  |

| Bit 10     | Video Stream Serial Interrupt flag0No interrupt1Interrupt outstanding                       |

| Bit 11     | Video DDC Interrupt Flag<br>0 No interrupt<br>1 Interrupt outstanding                       |

| Bit 12     | VideoStream External Interrupt flag0No interrupt1Interrupt outstanding                      |

| Bits 13-30 | Reserved<br>Read as zero                                                                    |

| Bit 31     | SVGA Interrupt flag<br>0 No interrupt<br>1 Interrupt asserted                               |

### 3.2.4 Input FIFO Space Register

The input FIFO space register indicates the number of words that can currently be written to the input FIFO. This register can be read at any time and used to allow the controlling software to efficiently send data to the PERMEDIA . If the DMA controller for the FIFO is in use, the value read is a snapshot of the current FIFO status.

## InFIFOSpace

| Region: |    |   | Ζ | er | С   |                 |    |   |   |   |   |    | Re | ad  |    |     |      |      |     |     |     |     |    |    |   |   |   |   |    |   |   |

|---------|----|---|---|----|-----|-----------------|----|---|---|---|---|----|----|-----|----|-----|------|------|-----|-----|-----|-----|----|----|---|---|---|---|----|---|---|

| Offset: |    |   | 0 | 00 | 0.0 | )0 <sup>.</sup> | 18 | h |   |   |   |    | Re | set | Va | alu | e:   |      |     | 00  | )00 | ).C | 00 | 20 | h |   |   |   |    |   |   |

|         | 31 |   |   |    |     |                 | 2  | 4 |   |   |   |    |    |     | 16 | 5   |      |      |     |     |     |     | 8  | 3  |   |   |   |   |    |   | 0 |

|         |    |   |   | T  |     |                 | I  |   | 1 | I |   | -r | I  |     | I  |     |      | I    | T   |     | 1   |     |    |    | 1 | T |   |   | T  |   |   |

|         |    |   |   |    |     |                 |    |   |   |   |   |    | In | put | FI | FC  | ) Av | /ail | lab | ole |     |     |    |    |   |   |   |   |    |   |   |

|         | Ĺ  | Ĺ | j | İ. | Ĺ   | j               | j  | j | j | j | j | j  | j  | 1   | j  | İ   | j    | İ    | İ   | İ.  | İ   | İ.  | j  | ĺ  | j | ĺ | j | Ĺ | İ. | j | i |

Bits 0-31

Input FIFO Space

The number of empty words in the input FIFO. This number of words can be written before checking again for FIFO space availability.

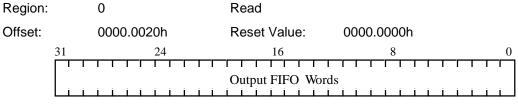

### 3.2.5 Output FIFO Words Register

The output FIFO words register indicates the number of words currently in the output FIFO. This register can be read at any time and used to allow the controlling software to efficiently read output data from the PERMEDIA.

## OutFIFOWords

Bits 0-31 Output FIFO Words

The number of valid words in the output FIFO. This number of words can be read before checking for more words.

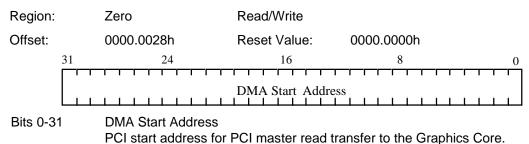

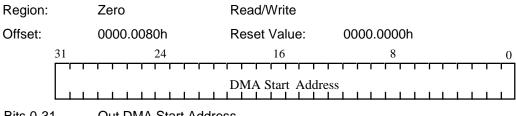

#### 3.2.6 In DMA Start Address

The DMA address should be loaded with the first PCI address for the buffer to be transferred to the GC when using the DMA controller.

Writing to the DMA count register loads the address into the DMA counter. Once a DMA has been set off the next DMA start address may be loaded. A read of this register returns the last start value loaded even if the DMA is underway.

## DMAAddress

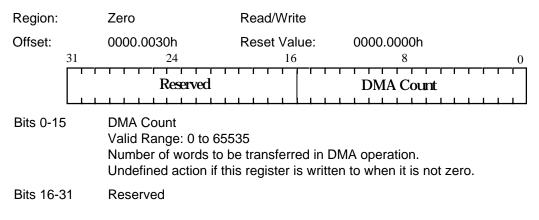

#### 3.2.7 In DMA Count

The DMA count register should be loaded with the number of words to be transferred in the DMA operation. The action of loading a word count greater than zero sets off the DMA operation. The value read back from this register indicates the current number of words left to be transferred.

This register should only be written to if the count is zero. It can be read at any time.

### **DMACount**

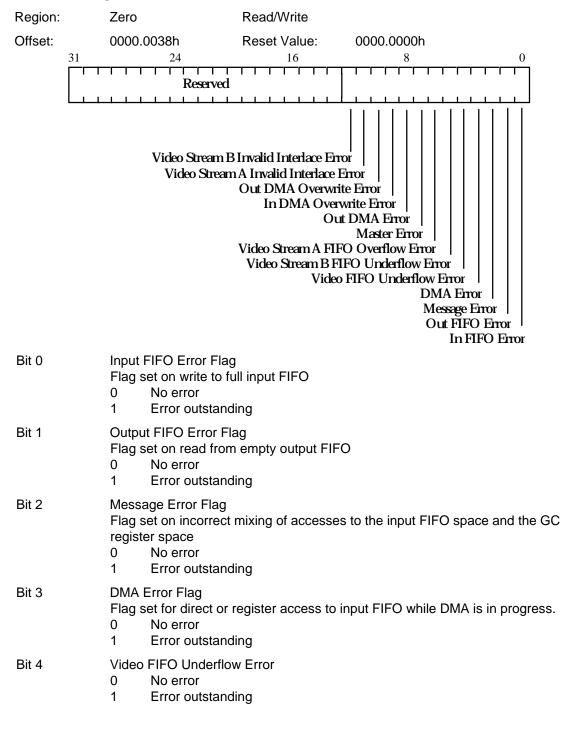

### 3.2.8 Error Flags Register

The Error Flags Register shows which errors are outstanding on PERMEDIA .

Flag bits are reset by writing to this register with the corresponding bit set to a 1. Flags at positions where the bits are set to 0 will be unaffected by the write.

## ErrorFlags

| Bit 5      | 0 1              | itream B FIFO Underflow Error<br>No error<br>Error outstanding                                                                       |

|------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Bit 6      | 0 1              | tream A FIFO Overflow Error<br>No error<br>Error outstanding                                                                         |

| Bit 7      | 0 1              | Error<br>aster abort or target abort occurs as a consequence of a master access.<br>No error<br>Error outstanding                    |

| Bit 8      | OutDMA<br>0 N    | A Error<br>ave access is made to output FIFO while DMA is in progress (i.e.<br>ACount is not zero).<br>No error<br>Error outstanding |

| Bit 9      | Set if In<br>0 N | Overwrite Error<br>DMACount register is written when it is not zero.<br>No error<br>Error outstanding                                |

| Bit 10     | Set if C<br>0 N  | A Overwrite Error<br>DutDMACount register is written when it is not zero.<br>No error<br>Error outstanding                           |

| Bit 11     | Set for i<br>0 N | tream A Invalid Interlace Error<br>nvalid sequence of fields.<br>No error<br>Error outstanding                                       |

| Bit 12     | Set for i<br>0 N | tream B Invalid Interlace Error<br>nvalid sequence of fields.<br>No error<br>Error outstanding                                       |

| Bits 13-31 | Reserve          | ed                                                                                                                                   |

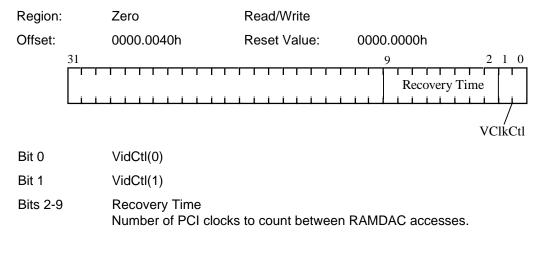

### 3.2.9 Video Clock Control Register

Vidctl 0 and 1 select the DClk PLL registers to use. An eight-bit field is provided in this register to program the number of PCI clocks to be counted between each RAMDAC access.

## VClkCtl

(Read Only)

Bits 10-32 Reserved - Read as zero

### 3.2.10 Test Register

Writes to this register have an undefined effect.

### TestRegister

### 3.2.11 Aperture 1 Control Register

### ApertureOne

### 3.2.12 Aperture 2 Control Register

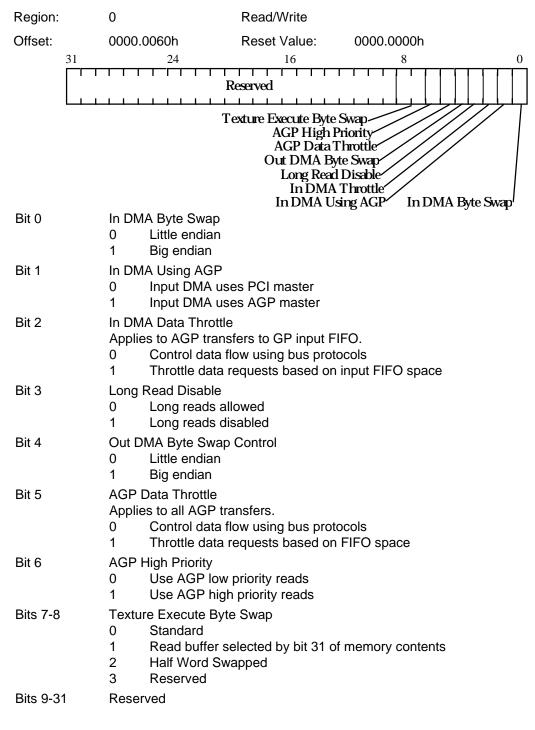

#### 3.2.13 DMA Control

The DMA control Register sets up the data transfer modes for the DMA controller. The DMA controller can be set to little endian or big ( byte swapped ) endian.

### **DMAControl**

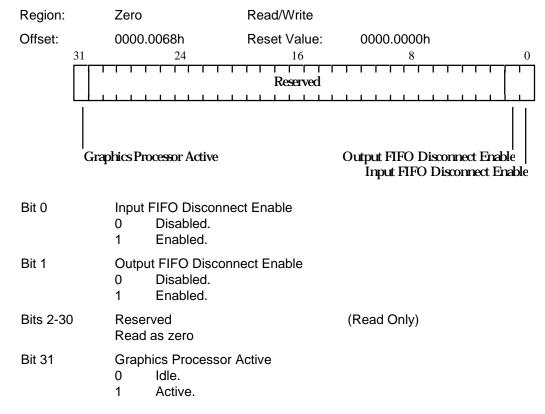

### 3.2.14 FIFO Disconnect

The FIFO disconnect register enables the input and output FIFO disconnect signals, which drive two physical pins on PERMEDIA. Disconnects are disabled at reset.

## FIFODiscon

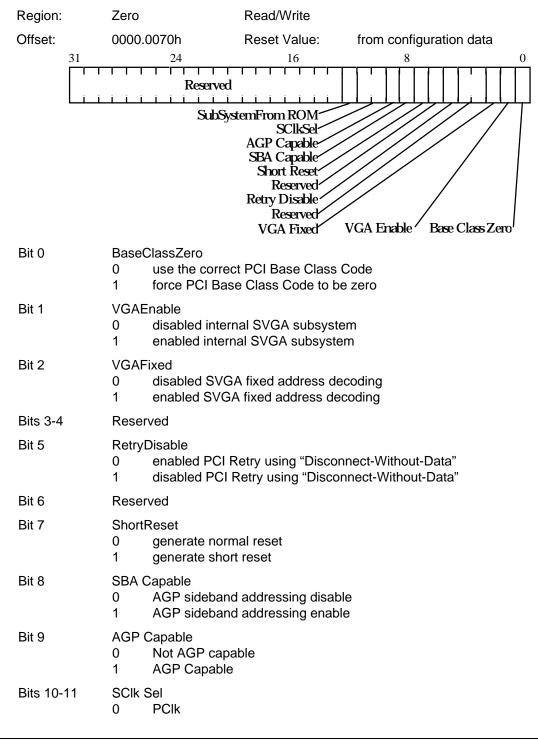

### 3.2.15 Chip Configuration

Most of the sampled values from the configuration pins are loaded into this register on the trailing edge of reset. This register can then be read back over the PCI bus to allow the host to determine how PERMEDIA has been configured and to modify fields of the configuration if required.

## ChipConfig

|            | 1 PClk/2<br>2 MClk<br>3 MClk/2                                          |                                                      |

|------------|-------------------------------------------------------------------------|------------------------------------------------------|

| Bit 12     | Sub System From ROM0Leave subsystem registers1Load sub system registers | s at reset state<br>from ROM immediately after reset |

| Bits 13-31 | Reserved<br>Read as zero                                                | (Read Only)                                          |

#### 3.2.16 Out DMA Start Address

The DMA address should be loaded with the first PCI address for the buffer to be transferred into from the GCd when using the DMA controller.

Writing to the DMA count register loads the address into the DMA counter. Once a DMA has been set off the next DMA start address may be loaded. A read of this register returns the last start value loaded even if the DMA is underway.

### **OutDMAAddress**

Bits 0-31 Out DMA Start Address

PCI start address for PCI master write transfer from the Graphics Core.

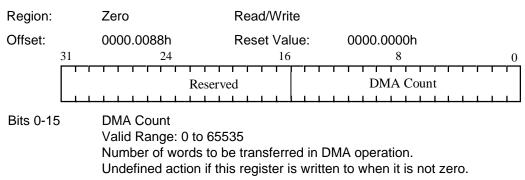

#### 3.2.17 Out DMA Count

The DMA count register should be loaded with the number of words to be transferred in the DMA operation. The action of loading a word count greater than zero sets off the DMA operation. The value read back from this register indicates the current number of words left to be transferred.

This register should only be written to if the count is zero. It can be read at any time.

## DMACount

Bits 16-31 Reserved

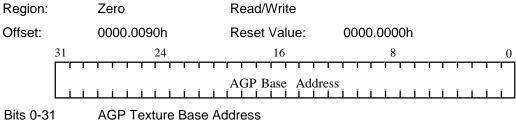

#### 3.2.18 AGP Texture Base Address

Base address of the texture in system memory. When a texture map is accessed directly from system memory the address in this register is added to the address generated by the Texture Read Unit in the Graphics Core.

## **AGPTexBaseAddress**

Bits 0-31

Base address in bytes for textures 'executed' from system memory.

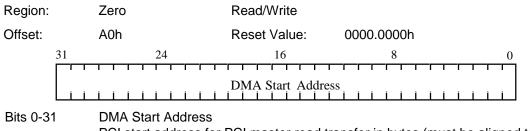

#### 3.2.19 Bypass DMA Start Address

The DMA address should be loaded with the first PCI address for the data to be transferred into the bypass by the DMA controller.

### **ByDMAAddress**

PCI start address for PCI master read transfer in bytes (must be aligned to 32 bits).

#### 3.2.20 Bypass DMAStride

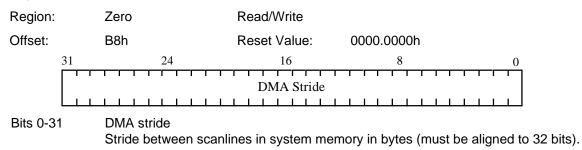

Sets the stride between scanlines of the data buffer to be transferred to by the bypass DMA controller.

## **ByDMAStride**

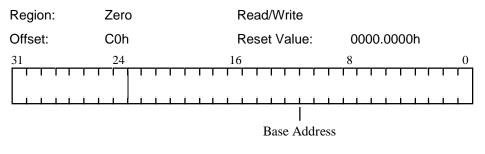

### 3.2.21 Bypass Memory Base Address

Sets the base address of the data buffer in PERMEDIA memory that data should be written to by the bypass DMA controller.

## ByDMAMemAddr

| Bits 0-23  | Base address<br>In natural data units (i.e. texels). |             |

|------------|------------------------------------------------------|-------------|

| Bits 24-31 | Reserved<br>(all bits zero)                          | (Read Only) |

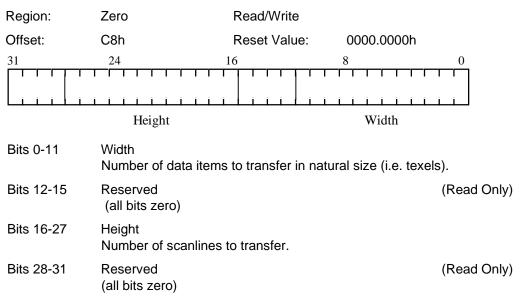

### 3.2.22 Bypass DMA Transfer Size

Sets the dimensions of the data buffer to be transferred by the DMA controller.

## **ByDMASize**

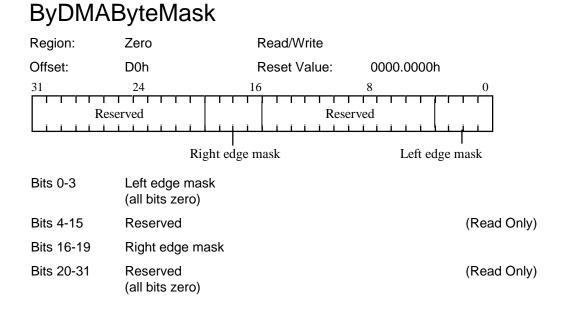

### 3.2.23 Bypass DMA Byte Mask

Masks the left and right edges of the data buffer transferred by the bypass DMA controller. The masks are applied to the 32 bit word at the start or end of the scanline as appropriate (the transfer is always done left to right).

0

### 3.2.24 Bypass DMA Control

Controls the operation of the bypass DMA controller.

#### **ByDMAControl** Read/Write Region: Zero Offset: D8h Reset Value: 0000.0000h 31 16 I 1 Ι PP0 Offset Y Offset X PP2 PP1 Patch Type Byte Swap Data Format Control Use AGP RestartGP Mode Mode Bits 0-1 0 Off 1 DMA (implicit auto addressing) 2 Aperture 1 auto addressing 3 Aperture 2 auto addressing Bit 2 RestartGP Do not restart graphics processor at end of DMA 0 Restart graphics processor at end of DMA 1 Bits 3-5 Data format 0 8 bits 1 16 bits 2 32 bits 3 4 bits 4 Y component - YUV planar mode 5 U component- YUV planar mode 6 V component- YUV planar mode Reserved 7 Bits 6-7 Patch Type 0 Patching disabled 1 Patch mode (8x8) 2 Sub-patch mode (32x32) Reserved 3 PP0 Bits 8-10 See table of partial product codes Bits 11-13 PP1 See table of partial product codes Bits 14-16 PP2 See table of partial product codes

| Bits 17-21 | Offset X<br>Added to X value in address calculatio                           | n           |

|------------|------------------------------------------------------------------------------|-------------|

| Bits 22-26 | Offset Y<br>Added to Y value in address calculatio                           | n           |

| Bits 27-28 | Byte Swap Control0Standard (no swap)1Byte swapped2Half word swapped3Reserved |             |

| Bits 29    | Use AGP<br>0 = Use PCI Master<br>1 = Use AGP Master                          |             |

| Bits 30-31 | Reserved<br>(all bits zero)                                                  | (Read Only) |

### 3.2.25 Bypass DMA Complete

Writing to this address indicates that the bypass load operations are complete and the graphics processor should be restarted. This is the manual version of RestartGP in ByDMAControl.

### **ByDMAComplete**

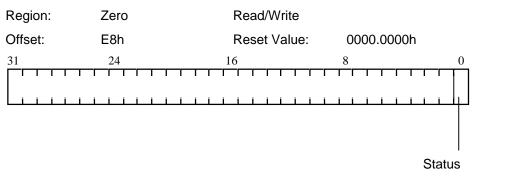

| Bits 0 | Status                                                    | (Read only) |

|--------|-----------------------------------------------------------|-------------|

|        | Reading this field returns the status of the texture inva | lid flag.   |

|        | 0 Texture Valid                                           |             |

|        | 1 Texture Invalid Flag set.                               |             |

|        |                                                           |             |

Bits 1-31 Read as zero, write data ignored

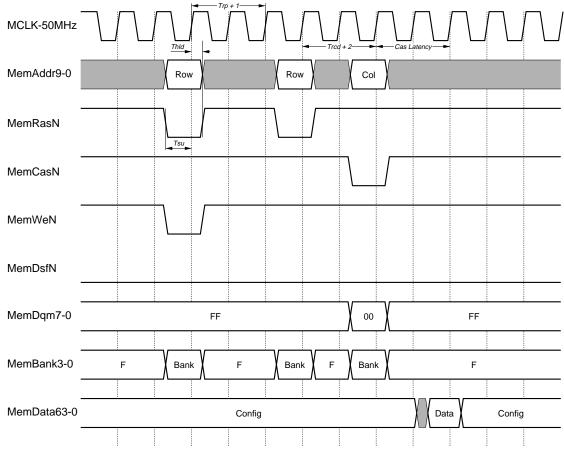

#### 3.3 Memory Control Registers

Refer to the memory system section for details on programming the memory control registers.

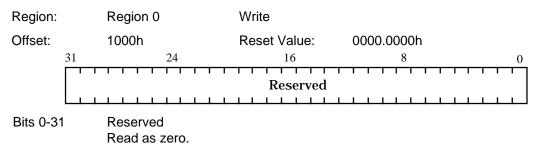

#### 3.3.1 Re-Boot

Writing to this address instructs the memory controller to reboot the SGRAMs. This involves going through the reset sequence and loading the Boot Address register. A re-boot does not reload the configuration data; registers maintain their contents until a reset. A read from this register returns zero.

### Reboot

### 3.3.2 Memory Control

### MemControl

Read as zero.

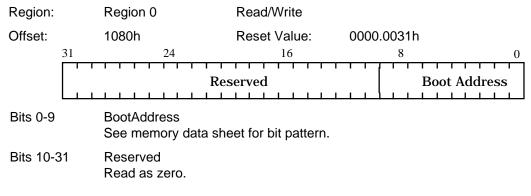

#### 3.3.3 Boot Address

The boot address value specifies the contents of the SGRAM mode register at boot time. Boot time is either at chip reset or the reboot caused by writing to a register.

### **BootAddress**

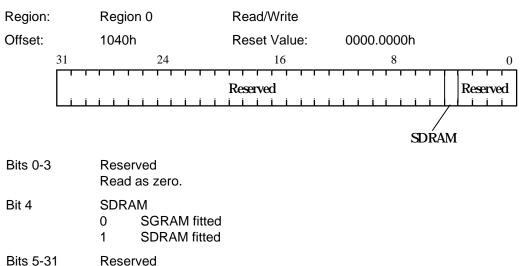

### 3.3.4 Memory Configuration

This register holds configuration data for the memory controller. If it is written to there is an automatic reboot of the memory. The correct sequence is to load the boot address, then change this register to match the boot address.

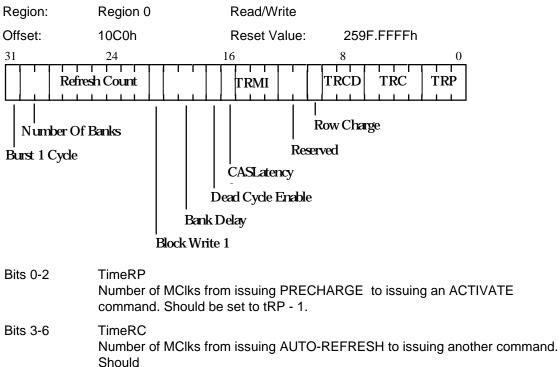

# MemConfig

be set to tRC - 2.

| Bits 7-9   | TimeRCD<br>Number of MClks from issuing RAS to issuing CAS. Should be set to tRCD - 2.                                                                  |  |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit 10     | RowCharge<br>0 row charge disabled<br>1 row charge enabled                                                                                              |  |  |  |  |  |

| Bits 11-12 | Reserved                                                                                                                                                |  |  |  |  |  |

| Bits 13-15 | TimeRASMin<br>Number of active clocks for the minimum Row Active time. Should be set to<br>tRAS -<br>3 unless this results in a value of zero.          |  |  |  |  |  |

| Bit 16     | CASLatency<br>0 CAS latency of 2.<br>1 CAS latency of 3.                                                                                                |  |  |  |  |  |

| Bit 17     | <ul> <li>DeadCycleEnable</li> <li>0 do not insert dead cycle between reads and writes</li> <li>1 insert dead cycle between reads and writes.</li> </ul> |  |  |  |  |  |

| Bits 18-20 | BankDelay<br>Defines read burst length. Should be set to burst length - 1.                                                                              |  |  |  |  |  |

| Bit 21     | Block Write 10do not allow single cycle block write operations1allow single cycle block write operations                                                |  |  |  |  |  |

| Bits 22-28 | RefreshCount<br>Defines period between AUTO-REFRESH commands. The count is in MClks/32.                                                                 |  |  |  |  |  |

| Bits 29-30 | NumberBanks<br>0 1 bank (2Mbytes)<br>1 2 banks (4Mbytes)<br>2 3 banks (6Mbytes)<br>3 4 banks (8Mbytes)                                                  |  |  |  |  |  |

| Bit 31     | <ul> <li>Burst1Cycle</li> <li>0 do not assume burst length of 1.</li> <li>1 assume burst length of 1.</li> </ul>                                        |  |  |  |  |  |

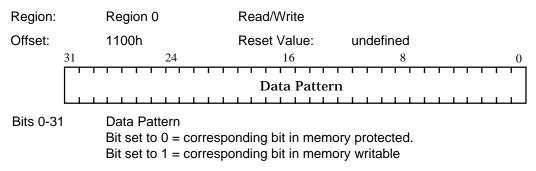

#### 3.3.5 Bypass Write Mask

Mask used to protect bits from modification by bypass writes to memory.

### **BypassWriteMask**

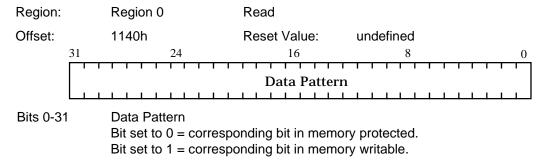

#### 3.3.6 Framebuffer Write Mask

Mask used to protect bits from modification by framebuffer writes to memory. Can be read from the bypass, but can only be modified through framebuffer write unit in the graphics core.

### FramebufferWriteMask

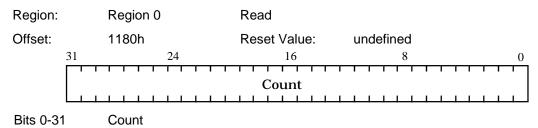

#### 3.3.7 Count

A free running count that may be used for any purpose. The counter is driven by MClk and wraps to zero at overflow.

### Count

#### 3.4 Video Control Registers

Refer to the video unit section for details on programming the video control registers.

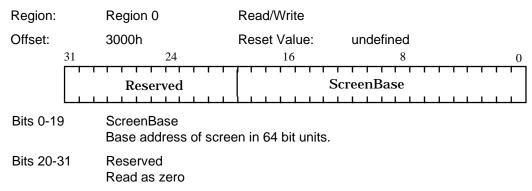

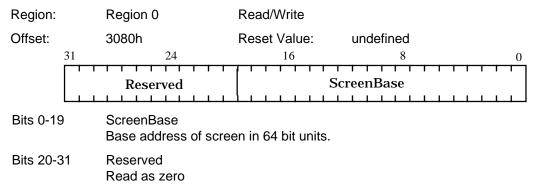

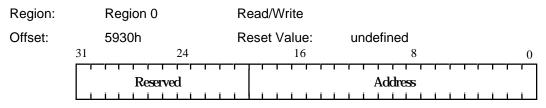

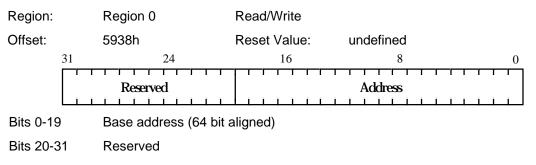

#### 3.4.1 Screen Base

Address of pixel in top left of screen. The value of this register is ignored until vertical blank. When it is loaded the BypassPending bit is set in the VideoControl register until it is used.

This register must be loaded after the HgEnd register.

### ScreenBase

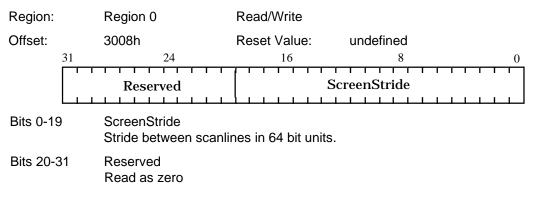

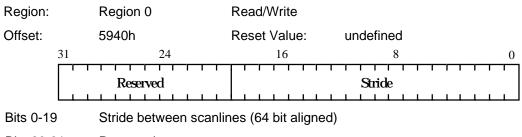

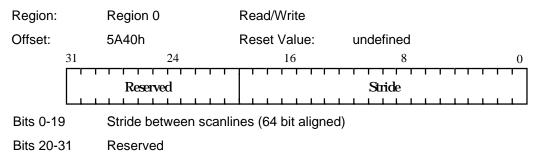

#### 3.4.2 Screen Stride

Stride between scanlines of display.

### ScreenStride

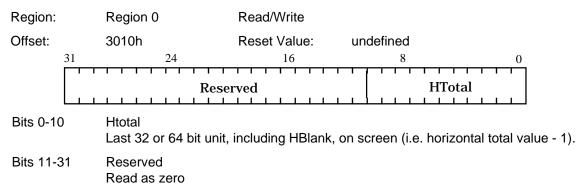

### 3.4.3 Horizontal Total

### HTotal

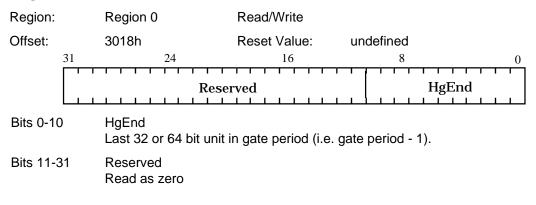

#### 3.4.4 Horizontal Gate End

The gate period defines the period during which video data is not clocked from PERMEDIA. The value of this register is not used until vertical blank.

## HgEnd

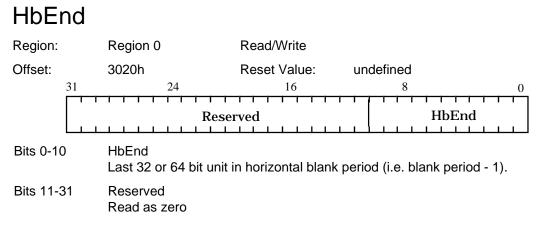

### 3.4.5 Horizontal Blank End

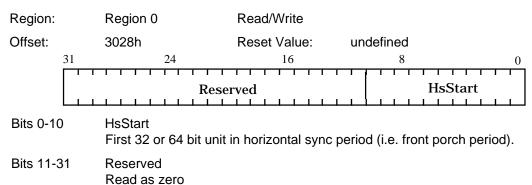

### 3.4.6 Horizontal Sync Start

### HsStart

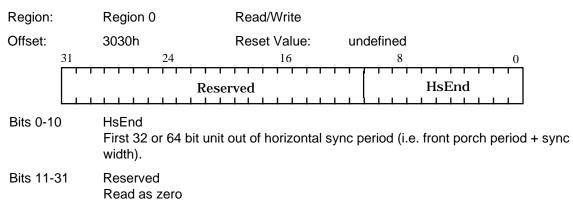

### 3.4.7 Horizontal Sync End

### HsEnd

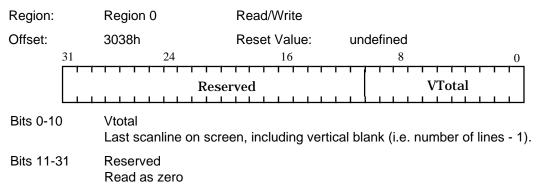

### 3.4.8 Vertical Total

### VTotal

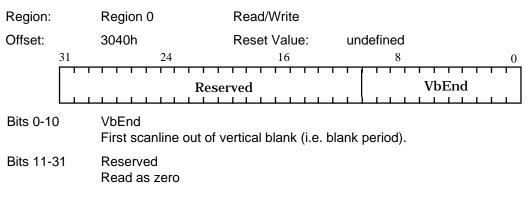

### 3.4.9 Vertical Blank End

### VbEnd

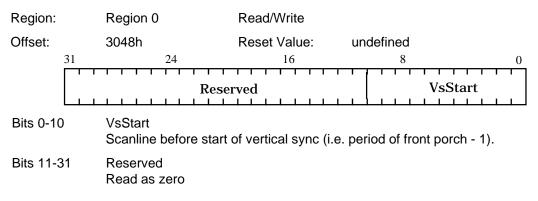

### 3.4.10 Vertical Sync Start

### VsStart

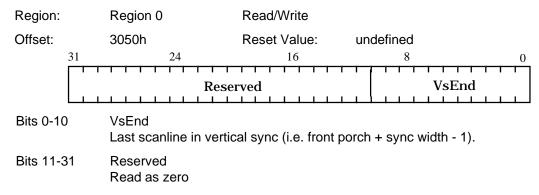

### 3.4.11 Vertical Sync End

### VsEnd

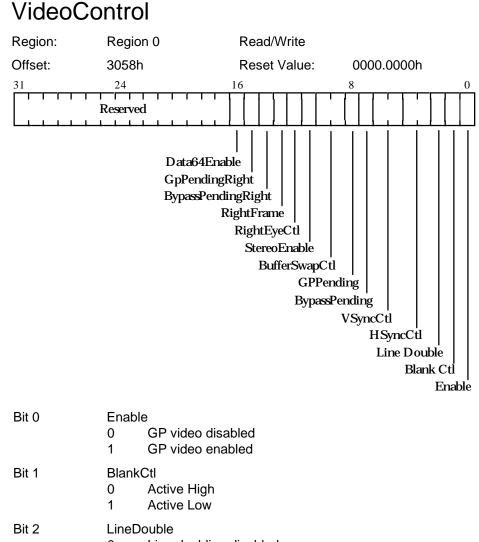

### 3.4.12 Video Control

- 0 Line doubling disabled

- 1 Line doubling enabled

|            | If enabled, each scanline is displayed twice to increase the effective frequency of low resolution screens.                                                                                                               |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits 3-4   | HSyncCtl<br>0 Forced High<br>1 Active High<br>2 Forced Low<br>3 Active Low                                                                                                                                                |

| Bits 5-6   | VSyncCtl<br>0 Forced High<br>1 Active High<br>2 Forced Low<br>3 Active Low                                                                                                                                                |

| Bit 7      | BypassPending0ScreenBase value used.1New ScreenBase value waiting to be used.Read only bit, set when ScreenBase is loaded through the bypass.                                                                             |

| Bit 8      | <ul> <li>GPPending</li> <li>0 ScreenBase value used.</li> <li>1 New ScreenBase value waiting to be used.</li> <li>Read only bit, set when ScreenBase is loaded through the Graphics Processor.</li> </ul>                 |

| Bits 9-10  | BufferSwapCtl0SyncOnFrameBlank1FreeRunning2LimitToFrameRate3Reserved                                                                                                                                                      |

| Bit 11     | StereoEnable<br>0 Disabled<br>1 Enabled                                                                                                                                                                                   |

| Bit 12     | RightEyeCtl<br>0 Active High<br>1 Active Low                                                                                                                                                                              |

| Bit 13     | RightFrame<br>0 Displaying left frame.<br>1 Displaying right frame.<br>Read only bit.                                                                                                                                     |

| Bit 14     | BypassPendingRight0ScreenBaseRight value used.1New ScreenBaseRight value waiting to be used.Read only bit, set when ScreenBaseRight is loaded through the bypass.                                                         |

| Bit 15     | <ul> <li>GPPendingRight</li> <li>ScreenBaseRight value used.</li> <li>New ScreenBaseRight value waiting to be used.</li> <li>Read only bit, set when ScreenBaseRight is loaded through the Graphics Processor.</li> </ul> |

| Bit 16     | <ul> <li>Data64Enable</li> <li>Data output to RAMDAC as 32 bit units.</li> <li>Data output to RAMDAC as 64 bit units.</li> </ul>                                                                                          |

| Bits 17-31 | Reserved                                                                                                                                                                                                                  |

Read as zero

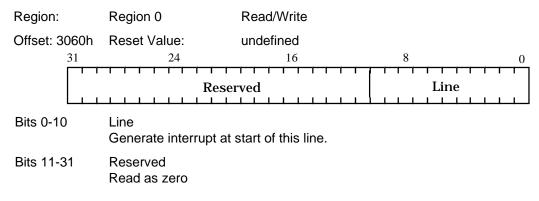

### 3.4.13 Interrupt Line

### InterruptLine

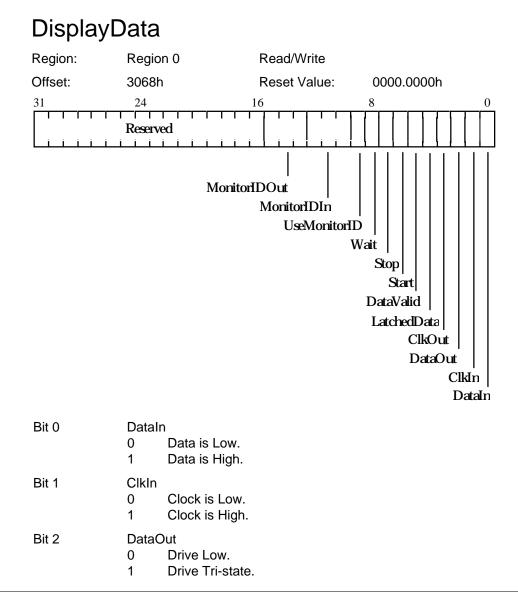

#### 3.4.14 Display Data

| Bit 3      | ClkOu<br>0<br>1           | it<br>Drive Low.<br>Drive Tri-state.                                                                                   |

|------------|---------------------------|------------------------------------------------------------------------------------------------------------------------|

| Bit 4      | Latche<br>0<br>1          | edData<br>Data latched at 0.<br>Data latched at 1.                                                                     |

| Bit 5      | Data∨<br>0<br>1<br>Cleare | ′alid<br>DataIn not valid.<br>DataIn valid.<br>ed by writing 1 to this bit.                                            |

| Bit 6      | Start<br>0<br>1<br>Cleare | DDC bus has not passed through Start state.<br>DDC bus has passed through Start state.<br>ed by writing 1 to this bit. |

| Bit 7      | Stop<br>0<br>1<br>Cleare  | DDC bus has not passed through Stop state.<br>DDC bus has passed through Stop state.<br>ed by writing 1 to this bit.   |

| Bit 8      | Wait<br>0<br>1            | Do not insert wait states in DDC.<br>Insert wait states.                                                               |

| Bit 9      | UseM<br>0<br>1            | onitorID<br>Use DDC.<br>Use monitor ID.                                                                                |

| Bits 10-12 | Monite<br>0<br>1          | orIDIn<br>Signal is Low.<br>Signal is High.                                                                            |

| Bits 13-15 | Monite<br>0<br>1          | orIDOut<br>Drive Low.<br>Drive Tri-state.                                                                              |

| Bits 16-31 | Reser<br>Read             | ved<br>as zero                                                                                                         |

### 3.4.15 Fifo Control

| FifoCon    | trol                                                                  |                                                                         |

|------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------|

| Region:    | Region 0                                                              | Read/Write                                                              |

| Offset:    | 3078h                                                                 | Reset Value: 0000.1010h                                                 |

| 31         | 24<br>Reserved<br>Underflow<br>Reserved<br>HighThr                    | 16 8 0<br>16 Reserved<br>LowThreshold                                   |

| Bits 0-4   | LowThreshold<br>Video data is access<br>or less spaces in the         | sed from memory at a low priority when there are this many video FIFO.  |

| Bits 5-7   | Reserved<br>Read as zero.                                             |                                                                         |

| Bits 8-12  | HighThreshold<br>Video data is access<br>or less spaces in the        | sed from memory at a high priority when there are this many video FIFO. |

| Bits 13-15 | Reserved<br>Read as zero.                                             |                                                                         |

| Bits 16    | Underflow<br>0 Underflow ha<br>1 Underflow ha<br>Cleared by writing 1 |                                                                         |

| Bits 17-31 | Reserved<br>Read as zero                                              |                                                                         |

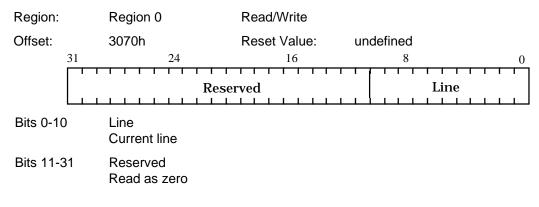

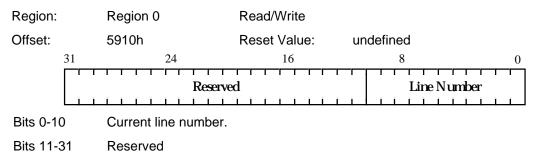

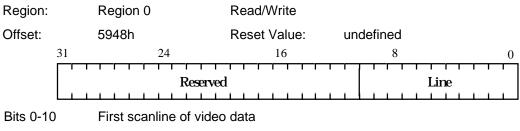

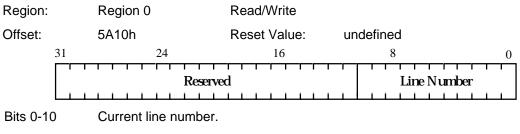

### 3.4.16 Line Count

### LineCount

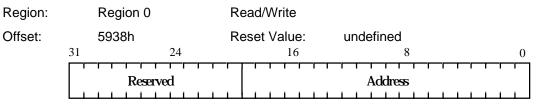

### 3.4.17 Screen Base Right

## ScreenBaseRight

#### 3.5 SVGA Interface

In addition to the standard SVGA registers, PERMEDIA supports two extended registers, the SVGA Control Register and the Mode 640 register.

#### 3.5.1 SVGA Memory

The SVGA memory is accessed through the SVGA legacy memory addresses. The SVGA memory can also be accessed through the PERMEDIA memory apertures by setting the 'SVGA access' bit in either the ApertureOne or ApertureTwo register. The memory address for the SVGA is formed from bits 16 down to 2 of the incoming bus address. This results in the 128K Byte SVGA memory space being aliased within the 8Mbyte total region size. No byte swapping or other data formatting is performed when accessing the SVGA memory in this manner.

#### 3.5.2 SVGA Registers

The PERMEDIA standard SVGA registers are accessed through the SVGA legacy IO addresses. These registers are also mapped into a 4K Byte space at offset 0x6000h in Region 0. The address for the SVGA unit is formed from bits 9 down to 2 of the incoming bus address. So, for example, SVGA register 0x3C4h can be addressed at offsets 0x63C4h, 0x67C4h, 0x6BC4h and 0x6FC4h.

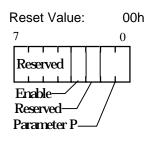

### 3.5.3 SVGA Control Register

This extended SVGA register is accessed as index 5 through the sequencer index register at port 0x3C4h. Data is written to port 3C5h.

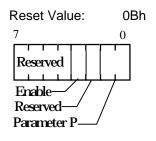

# VGAControlReg

| Region: | Region 0 F                                                     | Read/Write                                                                                        |

|---------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Offset: | F                                                              | Reset Value: 4Bh                                                                                  |

|         |                                                                |                                                                                                   |

| Bit 0   |                                                                | cess<br>cesses to memory.<br>esses to memory.                                                     |

| Bit 1   |                                                                | cesses to RAMDAC.<br>esses to RAMDAC.                                                             |

| Bit 2   | EnableInterrupts<br>0 Disable interrupt<br>1 Enable interrupts |                                                                                                   |

| Bit 3   |                                                                | isplay, enable graphics processor display.<br>splay, disable graphics processor display.          |

| Bit 4   | DacAddr2<br>Sets bit 2 of RAMDAC                               | address.                                                                                          |

| Bit 5   | DacAddr3<br>Sets bit 3 of RAMDAC a                             | address.                                                                                          |

| Bit 6   |                                                                | ing and producing sync pulses.<br>produce sync pulses. Only has effect when<br>s been set to zero |

| Bit 7   | Reserved<br>Read as zero                                       |                                                                                                   |

### 3.5.4 Mode 640 Register

This extended SVGA register is accessed as index 9 through the graphics index register at port 3CEh. Data is written to port 3CFh.

## Mode640Reg

| Region:  | Region 0 Read/Write                                                      |

|----------|--------------------------------------------------------------------------|

| Offset:  | Reset Value: 00h                                                         |

|          | 7 0<br>BankB BankA<br>Display start address bit<br>Enable                |

| Bits 0-2 | BankA<br>Additional address bits for accesses between A0000h and B0000h. |

| Bits 3-5 | BankB<br>Additional address bits for accesses between B0000h and C0000h. |

| Bit 6    | Bit 16 of display start address<br>Read as zero.                         |

| Bit 7    | Enable<br>0 Mode640 disabled.<br>1 Mode640 enabled.                      |

### 3.5.5 Video Streams Registers

Refer to the video streams section for details on programming these registers.

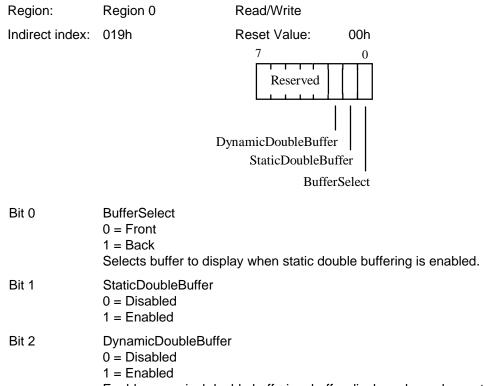

#### **VSConfiguration** Region 0 Read/Write Region: Offset: 5800h Reset Value: 0000.01F0h 24 8 31 16 0 Т ROMPulse Reserved DoubleEdgeB/ GPBusMode **ReverseDataB** UnitMode ColorSpaceB' HRefPolarityA InterlaceB' VRefPolarityA **VActiveVBIB** VActivePolarityA FieldEdgeB `UseFieldA FieldPolarityB' FieldPolarityA UseFieldB' `FieldEdgeA VActivePolarityB/ VActiveVBIA VRefPolarityB' HRefPolarityB ReverseDataA InterlaceA Bits 0-2 Unit mode Bit 3 **GPBusMode** 0 = Operate GP bus in Mode B 1 = Operate GP bus in Mode A Bits 4-8 **ROMPulse** Bit 9 **HRefPolarityA** 0 =Active low 1 = Active high Bit 10 VRefPolarityA 0 =Active low 1 = Active highVActivePolarityA Bit 11 0 =Active low 1 = Active high Bit 12 UseFieldA 0 = Disabled1 = Enabled Bit 13 FieldPolarityA 0 =Active low 1 = Active highBit 14 FieldEdgeA 0 = Inactive edge 1 = Active edge

| Bit 15     | VActiveVBIA<br>0 = Ignore VActive for VBI data<br>1 = Gate VBI data with VActive |

|------------|----------------------------------------------------------------------------------|

| Bit 16     | InterlaceA<br>0 = Video is not interlaced<br>1 = Video is interlaced             |

| Bit 17     | ReverseDataA<br>0 = Disabled<br>1 = Enabled                                      |

| Bit 18     | HRefPolarityB<br>0 = Active low<br>1 = Active high                               |

| Bit 19     | VRefPolarityB<br>0 = Active low<br>1 = Active high                               |

| Bit 20     | VActivePolarityB<br>0 = Active low<br>1 = Active high                            |

| Bit 21     | UseFieldB<br>0 = Disabled<br>1 = Enabled                                         |

| Bit 22     | FieldPolarityB<br>0 = Active low<br>1 = Active high                              |

| Bit 23     | FieldEdgeB<br>0 = Inactive edge<br>1 = Active edge                               |

| Bit 24     | VActiveVBIB<br>0 = Ignore VActive for VBI data<br>1 = Gate VBI data with VActive |

| Bit 25     | InterlaceB<br>0 = Video is not interlaced<br>1 = Video is interlaced             |

| Bit 26     | ColorSpaceB<br>0 = YUV<br>1 = RGB                                                |

| Bit 27     | ReverseDataB<br>0 = Disabled<br>1 = Enabled                                      |

| Bit 28     | DoubleEdgeB<br>0 = Disabled<br>1 = Enabled                                       |

| Bits 29-31 | Reserved                                                                         |

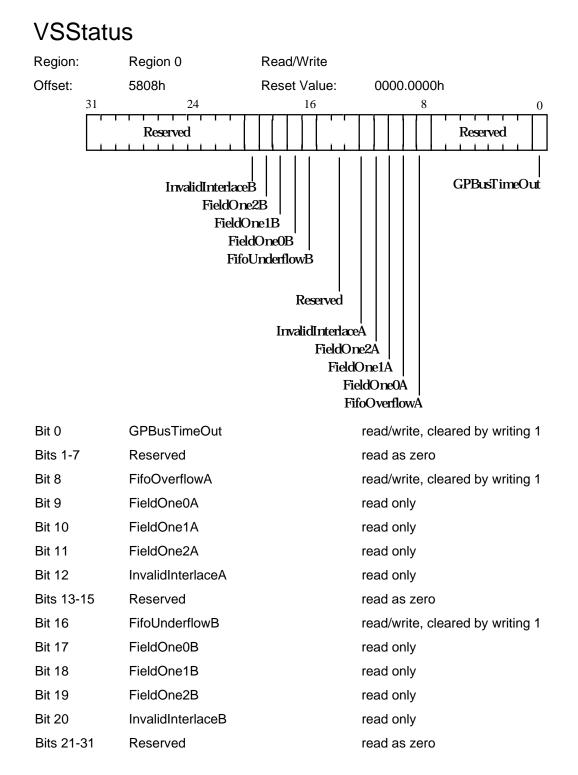

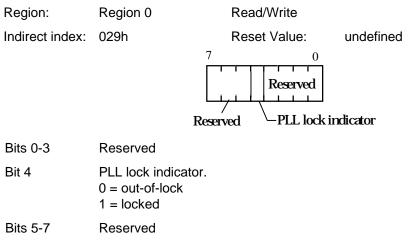

#### 3.5.6 VSStatus

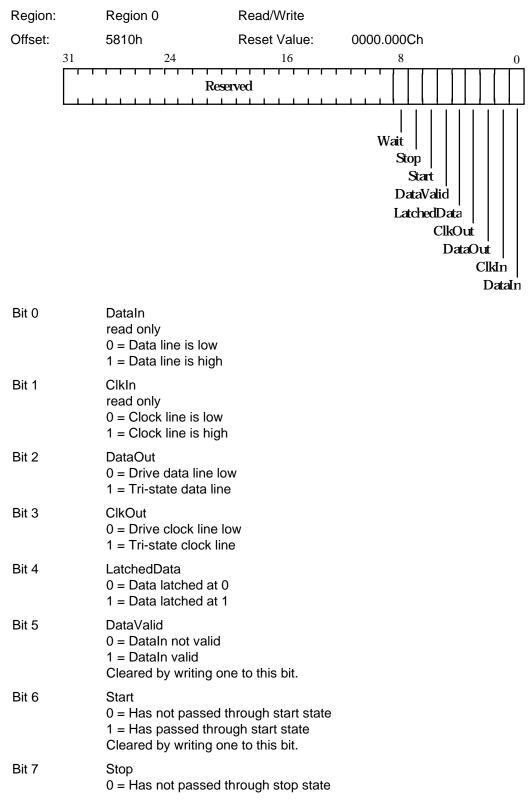

#### 3.5.7 VSSerialBusControl

### **VSSerialBusControl**

|           | 1 = Has passed through stop state<br>Cleared by writing one to this bit. |

|-----------|--------------------------------------------------------------------------|

| Bit 8     | Wait<br>0 = Do not insert wait states<br>1 = Insert wait states          |

| Bits 9-31 | Reserved<br>Read back as zero.                                           |

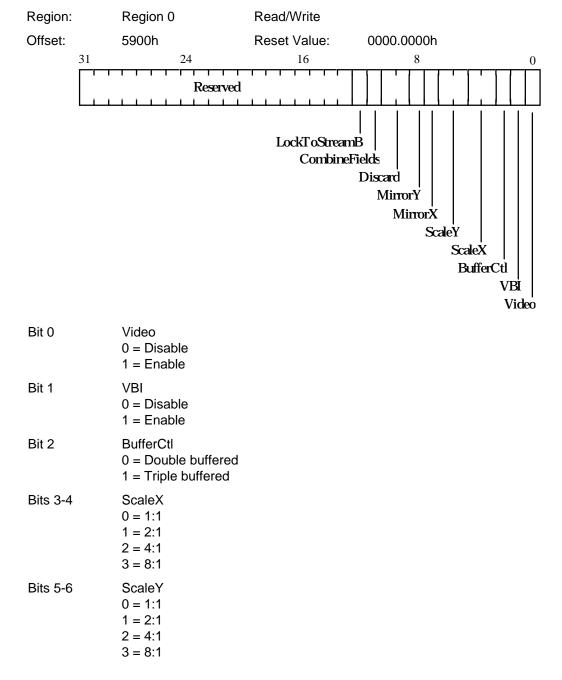

#### 3.5.8 VSAControl

## VSAControl

| Bit 7      | MirrorX<br>0 = Disable<br>1 = Enable                                |

|------------|---------------------------------------------------------------------|

| Bit 8      | MirrorY<br>0 = Disable<br>1 = Enable                                |

| Bits 9-10  | Discard<br>0 = None<br>1 = FieldOne<br>2 = FieldTwo<br>3 = Reserved |

| Bit 11     | CombineFields<br>0 = Disable<br>1 = Enable                          |

| Bit 12     | LockToStreamB<br>0 = Disable<br>1 = Enable                          |

| Bits 13-31 | Reserved                                                            |

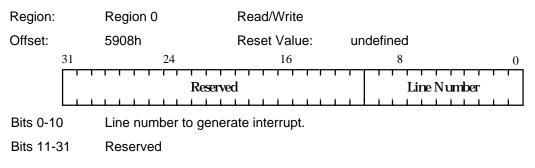

#### 3.5.9 VSAInterrupt

# VSAInterrupt

### 3.5.10 VSACurrentLine

### VSACurrentLine

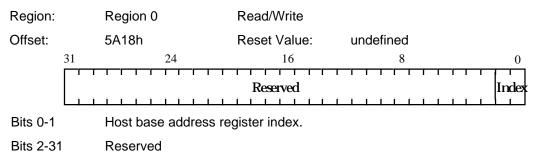

### 3.5.11 VSAVideoAddressHost

## VSAVideoAddressHost

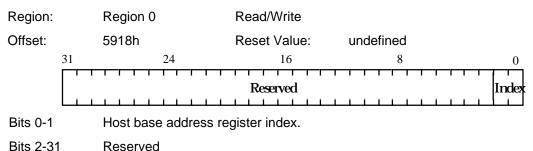

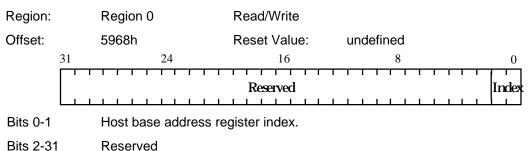

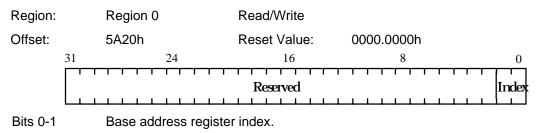

#### 3.5.12 VSAVideoAddressIndex

# VSAVideoAddressIndex

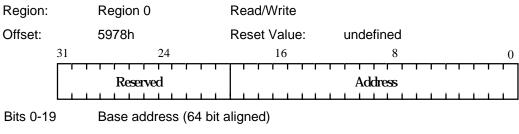

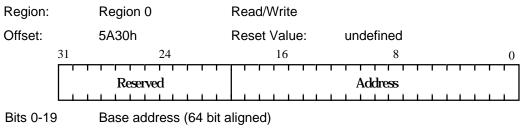

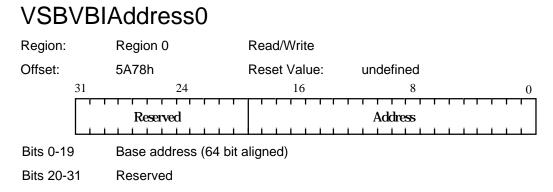

### 3.5.13 VSAVideoAddress0

### VSAVideoAddress0

- Bits 0-19 Base address (64 bit aligned)

- Bits 20-31 Reserved

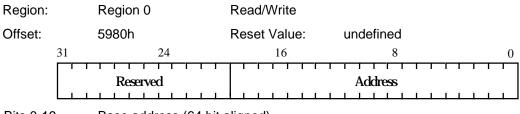

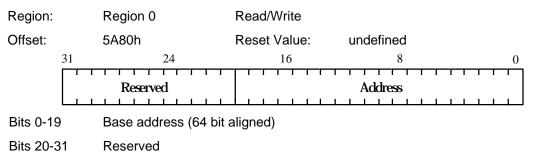

#### 3.5.14 VSAVideoAddress1

## VSAVideoAddress1

| Bits 0-19 | Base address (64 bit aligned) |

|-----------|-------------------------------|

|-----------|-------------------------------|

Bits 20-31 Reserved

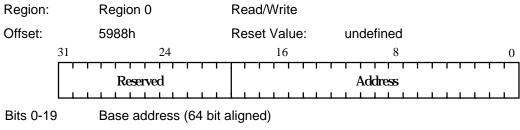

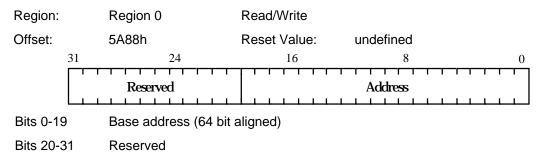

#### 3.5.15 VSAVideoAddress2

### VSAVideoAddress2

| Bits 0-19 | Rase address  | (64 bit aligned)  |

|-----------|---------------|-------------------|

| DIG 0 10  | Dube dual coo | (0+ bit ulighted) |

Bits 20-31 Reserved

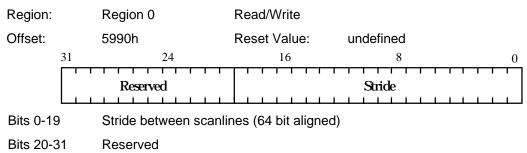

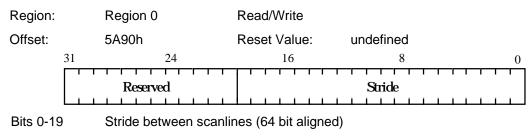

#### 3.5.16 VSAVideoStride

### VSAVideoStride

Bits 20-31 Reserved

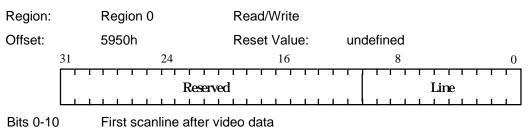

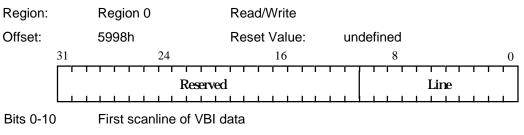

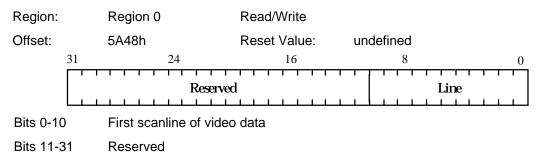

#### 3.5.17 VSAVideoStartLine

## VSAVideoStartLine

Bits 11-31 Reserved

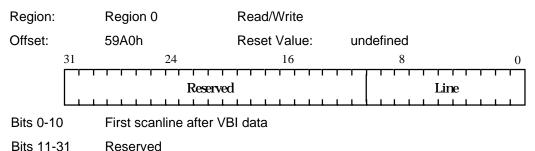

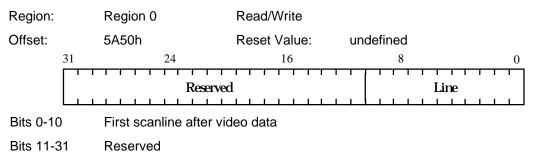

#### 3.5.18 VSAVideoEndLine

# VSAVideoEndLine

Bits 11-31 Reserved

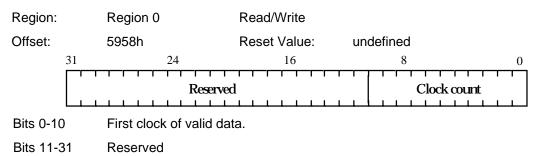

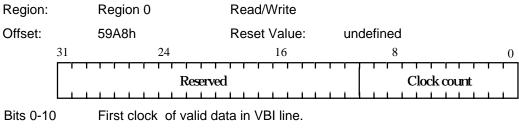

#### 3.5.19 VSAVideoStartData

### VSAVideoStartData

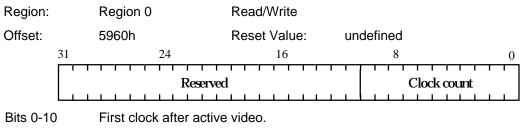

### 3.5.20 VSAVideoEndData

# VSAVideoEndData

Bits 11-31 Reserved

### 3.5.21 VSAVBIAddressHost

# VSAVBIAddressHost

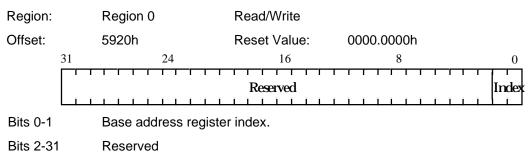

### 3.5.22 VSAVBIAddressIndex

### VSAVBIAddressIndex

#### 3.5.23 VSAVBIAddress0

Bits 20-31 Reserved

#### 3.5.24 VSAVideoAddress1

## VSAVBIAddress1

Bits 0-19 Base address (64 bit aligned)

Bits 20-31 Reserved

#### 3.5.25 VSAVBIAddress2

### VSAVBIAddress2

Bits 20-31 Reserved

### 3.5.26 VSAVBIStride

# VSAVBIStride

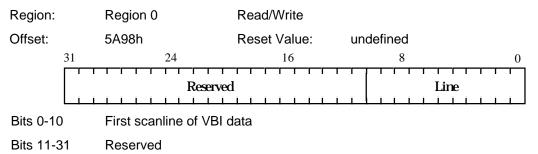

### 3.5.27 VSAVBIStartLine

# VSAVBIStartLine

Bits 11-31 Reserved

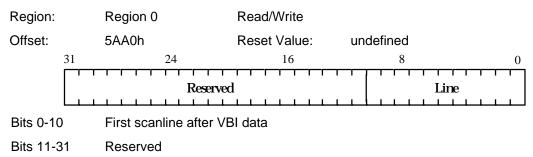

#### 3.5.28 VSAVBIEndLine

### VSAVBIEndLine

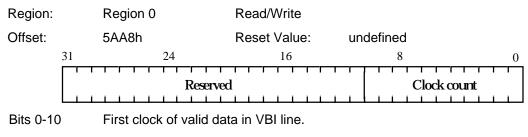

#### 3.5.29 VSAVBIStartData

### **VSAVBIStartData**

Bits 11-31 Reserved

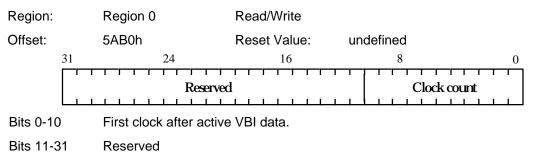

#### 3.5.30 VSAVBIEndData

## VSAVBIEndData

Bits 11-31 Reserved

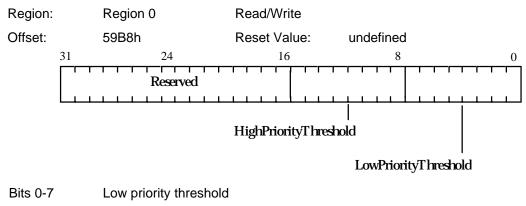

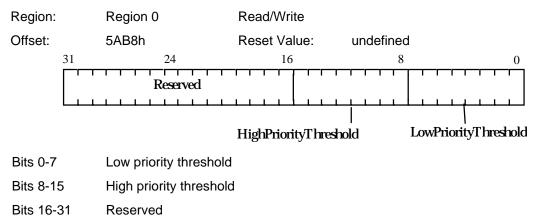

### 3.5.31 VSAFifoControl

### **VSAFifoControl**

- Bits 8-15 High priority threshold

- Bits 16-31 Reserved

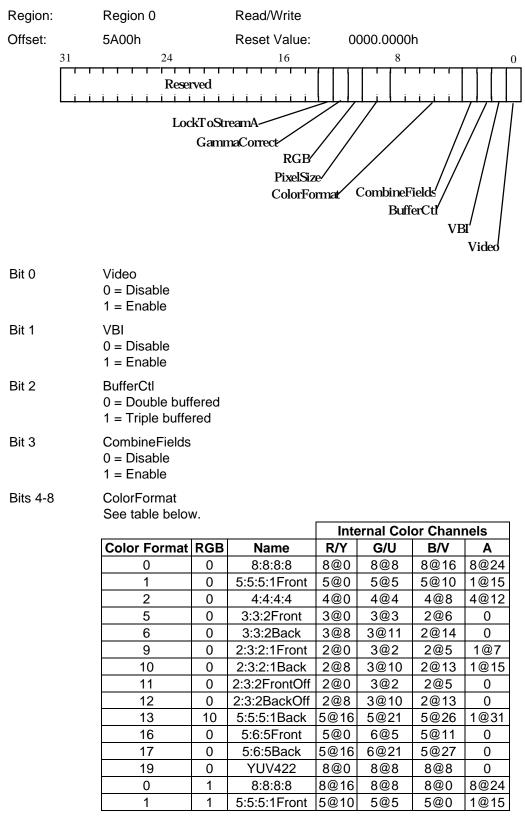

#### 3.5.32 VSBControl

### VSBControl

|            | 2                                                                           | 1 | 4:4:4:4       | 4@8  | 4@4  | 4@0  | 4@12 |

|------------|-----------------------------------------------------------------------------|---|---------------|------|------|------|------|

|            | 5                                                                           | 1 | 3:3:2Front    | 3@5  | 3@2  | 2@0  | 0    |

|            | 6                                                                           | 1 | 3:3:2Back     | 3@13 | 3@10 | 2@8  | 0    |

|            | 9                                                                           | 1 | 2:3:2:1Front  | 2@5  | 3@2  | 2@0  | 1@7  |

|            | 10                                                                          | 1 | 2:3:2:1Back   | 2@13 | 3@10 | 2@8  | 1@15 |

|            | 11                                                                          | 1 | 2:3:2FrontOff | 2@5  | 3@2  | 2@0  | 0    |

|            | 12                                                                          | 1 | 2:3:2BackOff  | 2@13 | 3@10 | 2@8  | 0    |

|            | 13                                                                          | 1 | 5:5:5:1Back   | 5@26 | 5@21 | 5@16 | 1@31 |

|            | 16                                                                          | 1 | 5:6:5Front    | 5@11 | 6@5  | 5@0  | 0    |

|            | 17                                                                          | 1 | 5:6:5Back     | 5@27 | 6@21 | 5@16 | 0    |

|            | 19                                                                          | 1 | YUV422        | 8@8  | 8@0  | 8@0  | 0    |

| Bits 9-10  | PixelSize<br>0 = 8 bits<br>1 = 16 bits<br>2 = 32 bits                       |   |               |      |      |      |      |

| Bit 11     | RGB<br>0 = BGR color<br>1 = RGB color                                       |   |               |      |      |      |      |

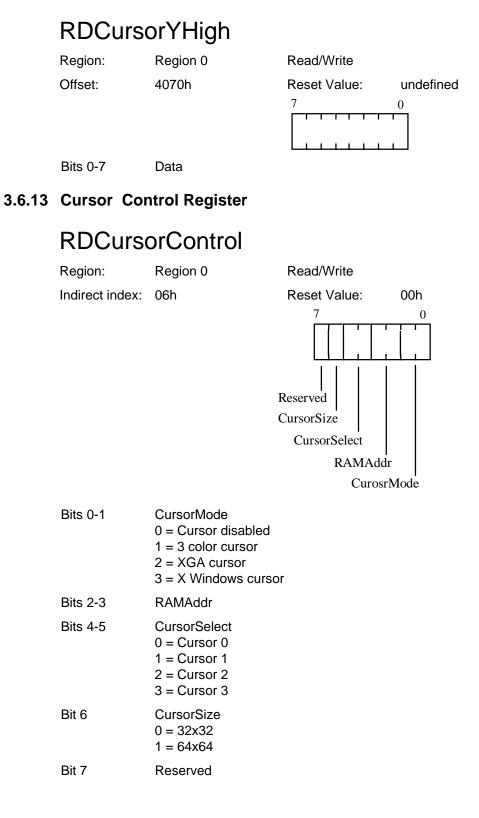

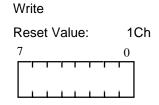

| Bit 12     | GammaCorrect<br>0 = Disable Gamma correction<br>1 = Enable Gamma correction |   |               |      |      |      |      |