## **PRELIMINARY DATA SHEET** July; 1989

## FEATURES

- Direct interface to dual-line, dual panel LCDs

- · Full backwards compatibility at the hardware level

- 256 color modes mapped to 32 gray shades on LCD

- Text & graphics scaling to fit LCD resolution

- Programmable for 8 or 16 bit PC bus interface

- Hardware graphics pointer and caret

- Fully compatible with GD510A/520A VGA chipset

- Software selectable support for LCD, Plasma, EL and digital/analog CRT displays

- Intelligent 8/16 bit Video Memory read/write interface from the microprocessor

- Can work with multi-frequency synthesizer IC

- 32 bit non-multiplexed Video Memory interface

- Supports eight 64kx4 or eight 256kx4 DRAMs, or four 128Kx8 pseudo-static RAMs.

- Support for system power down modes

- 16 ICs including RAM for motherboard VGA

- Can share video memory & RAMDAC with graphics coprocessor (eg 34010)

- Advanced low power CMOS technology

## *CL – GD 610/620*

## Flat Panel/CRT Enhanced VGA Controller

### **OVERVIEW**

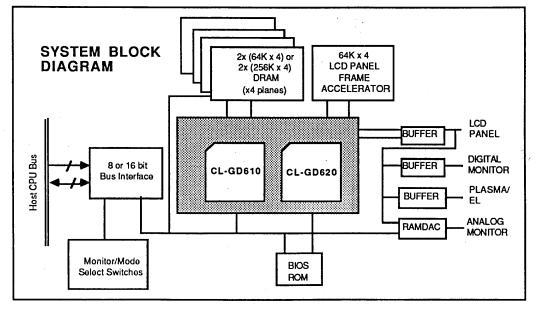

The CL-GD610 Graphics/Attributes chip and the CL-GD620 Sequencer/CRT Controller chip are enhanced versions of the CL-GD510A/520A VGA chipsets and continue to be hardware compatible with the IBM® VGA, EGA, CGA, and MDA standards, as well as with the Hercules<sup>®</sup> HGC at all levels-register, data path and BIOS. In addition, these chips may be used with a variety of flat panel displays as well as all popular CRT displays (CD, MD, ECD, PS/2, Variable frequency).

Monochrome LCD panels are driven by duty cycle modulation techniques to yield 16 gray scales with no screen flickering or stability problems. In addition, CIRRUS LOGIC's AutoMap<sup>TM</sup> technique automatically maps 256 colors into as many as 32 shades of gray for CRT quality gray scale emulation. Foreground/background color attributes are remapped automatically for maximum contrast. Expanded Text and Graphics modes provide larger character fonts and the ability to fill a panel (via ratiometrically determined scanline replication) even with low-resolution video modes. If expanded modes are not desired, automatic screen centering is performed. Panning/data compression allows viewing of 720 column modes on 640 column panels.

(cont'd on next page)

314610-001

## **OVERVIEW** (cont'd)

Operating at dot clock rates up to 33 MHz, the CL-GD610/620 chip set supports high resolution graphics and alphanumeric display modes for both monochrome and color, and for high resolution variable frequency and PS/2 monitors. Refresh rates from 60Hz up to 160Hz are available.

CIRRUS LOGIC's proprietary technology provides greater contrast, reduced flicker, and lower power dissipation with dual-line, dual-panel 400 or 480 scanline LCD panels.

Video outputs to CRT displays are provided in 4 bits per pixel (all resolutions) and 8 bits per pixel (256 color modes). Using analog video output and an external palette, selection may be made from 256K colors.

Video outputs to flat panel displays are provided in dual-panel format (4 bits each to upper and lower panels). LCD panels may be directly driven.

Plasma panels may be driven by the CRT video signals. AutoMap<sup>TM</sup> (256 color to 32 gray scale mapping) will work with gas plasma panels that can support 16 gray shades.

The intelligent 8/16 bit Video Memory Interface detects memory map configurations that place adjacent bytes in adjacent memory locations and automatically configures the chipset as a 16 bit peripheral. 16 bit operation may also be configured by program control.

The CL-GD610/620 implements all control and data registers in the current graphics standards, including those of the 6845 CRT Controller. Flexible register write protect control and the ability to save/restore all registers are both key elements enabling the chipset to be used in a variety of operating system and application environments.

The sequencer design provides more video memory cycles for the CPU during the normal video refresh/display cycle. During display-blanked intervals, ALL memory cycles can be allocated to process CPU memory requests.

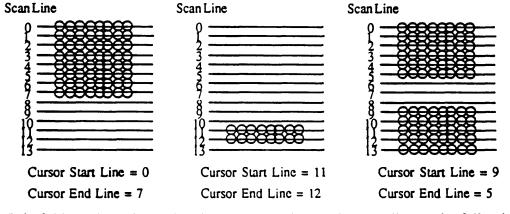

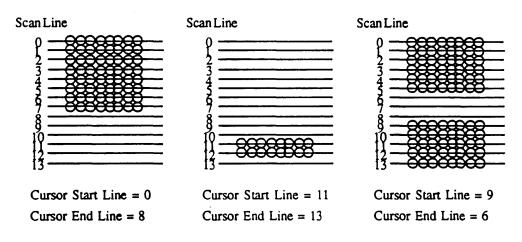

The hardware supports a mouse/graphics cursor, and a blinking insertion point text cursor. Additional text cursor controls include blink disable and replace/invert mode control. The hardware supports simultaneous and independent smooth scrolling of two separate text screens.

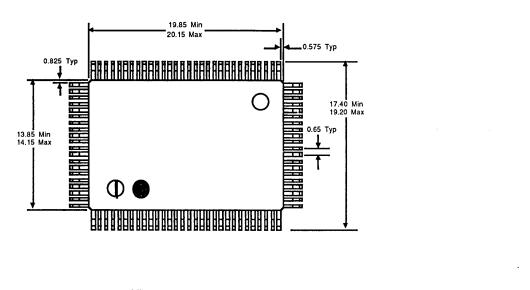

The CL-GD610/620 is designed for minimum external circuitry support and is ideal for integrated systems. For example, only 18 chips are necessary for a low-cost controller that can drive both a 640x480 LCD panel as well as a PS/2 monitor. No PALs are required with this dual 100-pin QFP chipset.

## Table of Contents

| 1                                                                                | PIN INFORMATION                                                      | .1                                                                                                                                     |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1.1                                                                              | Pin Diagram                                                          | .1                                                                                                                                     |

| 1.2                                                                              | Pin Assignment Table                                                 | .2                                                                                                                                     |

| 2                                                                                | DETAILED SIGNAL DESCRIPTION                                          | .4                                                                                                                                     |

| 2.1                                                                              | Processor Interface                                                  | .4                                                                                                                                     |

| 2.2                                                                              | Video Memory Interface                                               | .6                                                                                                                                     |

| 2.3                                                                              | Video Interface                                                      |                                                                                                                                        |

| 2.4                                                                              | External Interface                                                   | .8                                                                                                                                     |

| 2.5                                                                              | CL-GD610 / 620 Interconnect Signals                                  | .9                                                                                                                                     |

| 2.6                                                                              | LCD Display Frame Buffer Interface Signals                           |                                                                                                                                        |

| 3                                                                                | FUNCTIONAL DESCRIPTION                                               | 1                                                                                                                                      |

| 3.1                                                                              | Functional Operation                                                 |                                                                                                                                        |

| 3.2                                                                              | CRT Display Compatibility Modes                                      | 12                                                                                                                                     |

| 3.3                                                                              | Flat Panel Display Compatibility Modes                               |                                                                                                                                        |

| 3.4                                                                              | Supported Screen Formats                                             | 14                                                                                                                                     |

| 3.5                                                                              | LCD/CRT Screen Format Comparison Table                               | 16                                                                                                                                     |

| 4                                                                                | VGA,EGA,CGA, AND HGC REGISTER PORT MEMORY MAP 1                      | 7                                                                                                                                      |

| 5                                                                                | CGA, MDA, AND HGC REGISTERS 1                                        | <b>l 8</b>                                                                                                                             |

| 5.1                                                                              | Color Graphics Adapter (CGA) Compatible Registers                    | 18                                                                                                                                     |

| 5.2                                                                              | Monochrome Display Adapter (MDA) and Hercules Graphics Adapter (HGC) |                                                                                                                                        |

|                                                                                  |                                                                      |                                                                                                                                        |

|                                                                                  | Compatible Registers                                                 | 18                                                                                                                                     |

| 6                                                                                | VGA / EGA REGISTERS 1                                                | 19                                                                                                                                     |

| <b>6</b><br>6.1                                                                  | VGA / EGA REGISTERS                                                  | l 9<br>19                                                                                                                              |

| -                                                                                | VGA / EGA REGISTERS                                                  | l 9<br>19<br>20                                                                                                                        |

| 6.1                                                                              | VGA / EGA REGISTERS                                                  | 19<br>19<br>20<br>21                                                                                                                   |

| 6.1<br>6.2                                                                       | VGA / EGA REGISTERS                                                  | 19<br>19<br>20<br>21<br>22                                                                                                             |

| 6.1<br>6.2<br>6.3                                                                | VGA / EGA REGISTERS                                                  | <b>19</b><br>19<br>20<br>21<br><b>2</b> 2<br>22                                                                                        |

| 6.1<br>6.2<br>6.3<br>7<br>7.1<br>7.2                                             | VGA / EGA REGISTERS                                                  | 19<br>19<br>20<br>21<br>22<br>22<br>22                                                                                                 |

| 6.1<br>6.2<br>6.3<br>7<br>7.1                                                    | VGA / EGA REGISTERS                                                  | <ol> <li>9</li> <li>19</li> <li>20</li> <li>21</li> <li>22</li> <li>22</li> <li>22</li> <li>23</li> </ol>                              |

| 6.1<br>6.2<br>6.3<br>7<br>7.1<br>7.2                                             | VGA / EGA REGISTERS                                                  | <b>9</b><br>19<br>20<br>21<br><b>2</b><br>22<br>22<br>23<br><b>3</b><br><b>4</b>                                                       |

| 6.1<br>6.2<br>6.3<br>7<br>7.1<br>7.2<br>7.3<br><b>8</b><br>8.1                   | VGA / EGA REGISTERS                                                  | <b>19</b><br>20<br>21<br>22<br>22<br>22<br>23<br><b>34</b><br>34                                                                       |

| 6.1<br>6.2<br>6.3<br>7<br>7.1<br>7.2<br>7.3<br><b>8</b>                          | VGA / EGA REGISTERS                                                  | 19         20         21         22         22         22         23         34         35                                             |

| 6.1<br>6.2<br>6.3<br>7<br>7.1<br>7.2<br>7.3<br><b>8</b><br>8.1                   | VGA / EGA REGISTERS                                                  | 19         20         21         22         22         23         34         35         36                                             |

| 6.1<br>6.2<br>6.3<br>7<br>7.1<br>7.2<br>7.3<br>8<br>8.1<br>8.2<br>9<br>9.1       | VGA / EGA REGISTERS                                                  | 19         20         21         22         22         23         34         35         36         36                                  |

| 6.1<br>6.2<br>6.3<br>7<br>7.1<br>7.2<br>7.3<br>8<br>8.1<br>8.2<br>9<br>9.1<br>10 | VGA / EGA REGISTERS                                                  | 19         20         21         22         22         22         23         34         35         36         36         36         37 |

| 6.1<br>6.2<br>6.3<br>7<br>7.1<br>7.2<br>7.3<br>8<br>8.1<br>8.2<br>9<br>9.1       | VGA / EGA REGISTERS                                                  | 19         19         20         21         22         22         23         34         35         36         37                       |

`

·

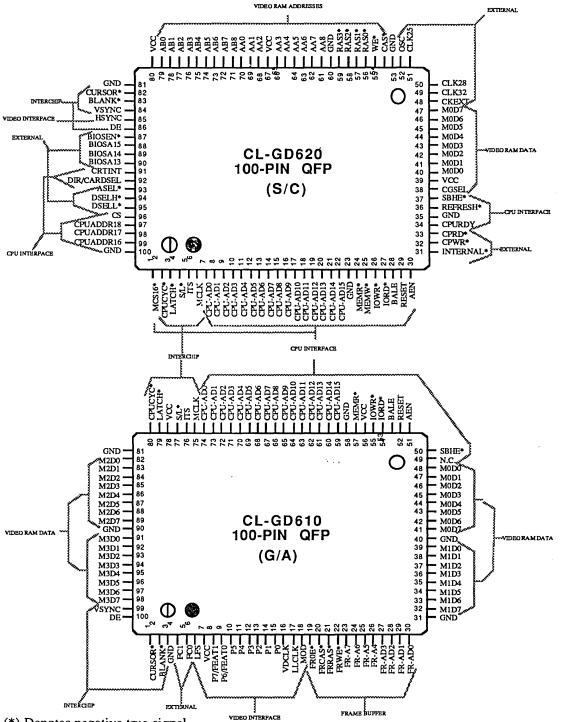

### 1 PIN INFORMATION

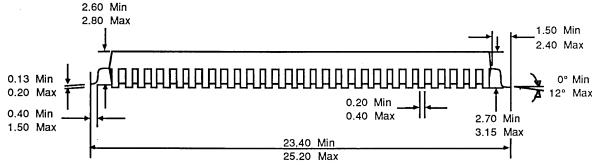

### 1.1 Pin Diagram

### 1.2 Pin Assignment Table

| NAME                        | GD610<br>PIN NO.  | GD620<br>PIN NO.    | ТҮРЕ                               | FUNCTION                                                                                      |

|-----------------------------|-------------------|---------------------|------------------------------------|-----------------------------------------------------------------------------------------------|

| PROCESSOR                   | INTERFACE         |                     |                                    |                                                                                               |

| SBHE*                       | 50                | 37                  | I-T                                | Bus High Enable from host CPU                                                                 |

| AEN                         | 51                | 30                  | I-T                                | DMA vs non-DMA bus cycles)                                                                    |

| RESET                       | 52                | 29                  | I-T                                | System Reset                                                                                  |

| BALE                        | 53                | 28                  | I-T                                | Buffered address latch enable from host CPU                                                   |

| IORD*,IOWR*                 | 54,55             | 27,26               | I-T                                | I/O R/W Strobes                                                                               |

| MEMR*,MEMV                  | V* 57             | 24,25               | I-T                                | CPU read/write of video memory                                                                |

| CPU-AD [15:0]               | 59-74             | 7-22                | I/O-T                              | Multiplexed CPU Address/Data/Switch bus                                                       |

| CPUADDR [18:                | 16]               | 97-99               | I-T                                | Upper 3 address bits from host CPU                                                            |

| CS                          |                   | 96                  | I-T                                | Memory decode of LA[23:19]                                                                    |

| DIR/CARDSEL                 | *                 | 92                  | O-T                                | Bidirectional CPU data bus transceiver control                                                |

| CRTINT                      |                   | 91                  | œ                                  | Display retrace interrupt                                                                     |

| REFRESH*                    |                   | 36                  | I-T                                | System refresh of bus attached RAM                                                            |

| CPURDY                      |                   | 34                  | 0<br>C                             | Data available signal for wait-state logic                                                    |

| MCS16*                      |                   | 1                   | Œ                                  | 16 bit peripheral access acknowledge                                                          |

|                             | ORY DATA IN       |                     | <b>TIO T</b>                       |                                                                                               |

| M0D[7:0]                    | 41-48             | 47-40               | I/O-T                              | Byte wide bidirectional data bus to Plane 0                                                   |

| M1D[7:0]                    | 32-39             |                     | I/O-T                              | Byte wide bidirectional data bus to Plane 1                                                   |

| M2D[7:0]                    | 82-89             |                     | I/O-T                              | Byte wide bidirectional data bus to Plane 2                                                   |

| M3D[7:0]<br>CGSEL (Attr bit | 91-98<br>3. M1D3) | 38                  | I/O-T<br>I-T                       | Byte wide bidirectional data bus to Plane 3<br>Selects alpha map                              |

|                             |                   |                     |                                    |                                                                                               |

|                             | ORY ADDRES        |                     |                                    |                                                                                               |

| CAS*                        |                   | 54                  | O-T                                | Column address strobe to all planes                                                           |

| WE*                         |                   | 55                  | O-T<br>O-T                         | Video memory write enable                                                                     |

| RAS[3:0]*                   | 61                | 56-59<br>-66, 68-70 | O-T<br>O-T                         | Row address strobe to planes 3-0                                                              |

| AA[8:0]<br>AB[8:0]          | 01                | 71-79               | О-Т<br>О-Т                         | Address bus to byte planes 0 and 1<br>Address bus to byte planes 2 and 3                      |

|                             |                   |                     | 01                                 |                                                                                               |

| EXTERNAL I                  | NTERFACE          |                     |                                    |                                                                                               |

| INTERNAL*                   |                   | 31                  | O-T                                | Selects internal vs. external video drivers.                                                  |

| CPWR*, CPRD                 | •                 | 32,33               | O-T                                | Color Palette write/read                                                                      |

| CKEXT                       | CI VOS            | 48                  | I/O-T                              | Input from ext clock (feat conn) or output to LCD panel                                       |

| CLK32, CLK28<br>OSC         | , CLK25           | 49-51               | I/O-T                              | Programmable pins, either clock select or clock inputs                                        |

| BIOSEN*                     |                   | 52<br>              | I-T<br>O-T                         | Oscillator input, MUST be connected to a clock                                                |

| BIOSA [15:13]               | · · · ·           | 88-90               | 0-1<br>0-T                         | BIOS ROM output enable select<br>BIOS page select (for 27C512 devices)                        |

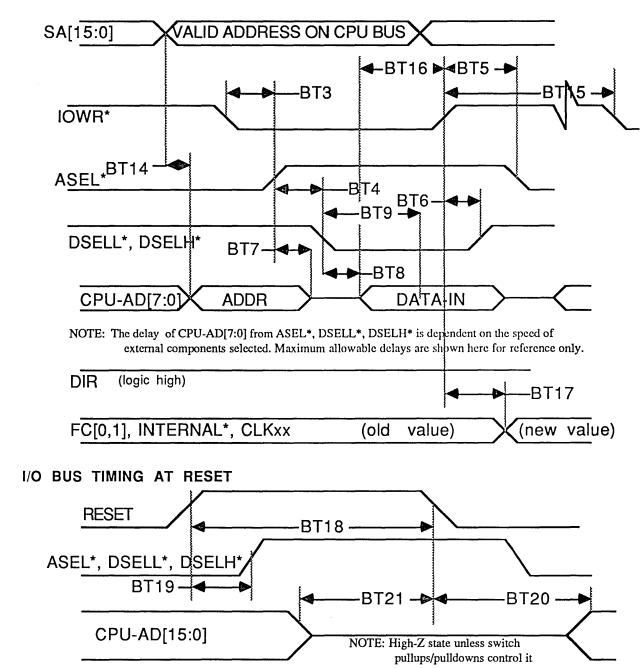

| ASEL*, DSELH                | * DSELL *         | 93-95               | O-T                                | Address and data sclect (low and high byte) enables                                           |

| FC [1:0]                    | 4,5               | 95-95               | O-T                                | Programmable, normally drive feature connector                                                |

| -                           |                   |                     | 01                                 |                                                                                               |

|                             | INTERCONN         |                     |                                    |                                                                                               |

| CURSOR*                     | 1                 | 82                  | GD620 to GD610-                    | · · · · · · · · · · · · · · · · · · ·                                                         |

| BLANK*                      | 2                 | 83                  | GD620 to GD610-                    | 0.0                                                                                           |

| MCLK                        | 75                | 6                   | GD620 to GD610-                    |                                                                                               |

| IIS<br>S/L *                | 76<br>77          | 5                   | GD620 to GD610-                    |                                                                                               |

| S/L*                        | 77<br>70          | 4                   | GD620 to GD610-                    |                                                                                               |

| LATCH*                      | 79                | 3<br>2              | GD620 to GD610-                    |                                                                                               |

| CPUCYC*<br>VSYNC            | 80<br>99          | 84                  | GD620 to GD610-<br>GD620 to GD610- |                                                                                               |

| DE                          | 100               | 86                  | GD620 to GD610-                    |                                                                                               |

| VIDEO INTE                  | DELCE             |                     |                                    | Analas ECD. CD. MDJ CD.                                                                       |

| VIDEO INTE                  |                   |                     |                                    | Analog ECD CD MD LCD                                                                          |

| LFS<br>P7/FF A T1           | 6                 |                     |                                    | D Frame Start<br>el Data MSB / Feature Bit 1 P7 UD3                                           |

| P7/FEAT1<br>P6/FEAT0        | 8<br>9            |                     |                                    | el Data MSB / Feature Bit 1 P7 UD3<br>el Data 6 / Feature Bit 0 P6 UD2                        |

| P5/SR                       | 10                |                     |                                    | el Data 5 / Secondary Red P5 SR UD1                                                           |

| P3/SK<br>P4/SG/I            | 10                |                     |                                    | el Data 4 / Second. Gr. / Intens P4 SG I UD0                                                  |

| P3/SB/V                     | 11                |                     |                                    | el Data 4 / Second. Ol. / Intens P4 SS I I ODO<br>el Data 3 / Second.Blue / Video P3 SB V LD3 |

| P2/R                        | 12                |                     |                                    | el Data 2 / Primary Red P2 R R LD2                                                            |

| P1/G                        | 15                |                     |                                    | el Data 1 / Primary Green P1 G G LD1                                                          |

| P0/B                        | 15                |                     |                                    | cl Data LSB / Primary Blue PO B B LDO                                                         |

|                             |                   |                     |                                    | •                                                                                             |

| NAME                                   | PIN NO.    | GD610<br>PIN NO. | GD620<br>TYPE | FUNCTION                           |

|----------------------------------------|------------|------------------|---------------|------------------------------------|

| VDCLK                                  | 16         |                  | 0-С           | Video Data Clock                   |

| LLCLK                                  | 17         |                  | 0-C           | LCD Line clock                     |

| MOD                                    | 18         |                  | 0-C           | LCD Modulation output              |

| HSYNC                                  |            | 70               | O-T           | Horizontal Sync output             |

| BUFFER MEI                             | MORY ADDRI | ESS INTERFA      | CE            |                                    |

| FROE*                                  | 19         |                  | O-T           | Buffer Output Enable               |

|                                        | 20         |                  | O-T           | Buffer CAS*                        |

| FRCAS*                                 | 20         |                  |               |                                    |

|                                        | 20         |                  | O-T           | Buffer RAS*                        |

| FRRAS*                                 | -          |                  | O-T<br>O-T    | Buffer RAS*<br>Buffer Write Enable |

| FRCAS*<br>FRRAS*<br>FRWE*<br>FR-A[7:4] | 21         |                  |               |                                    |

Note: Under the TYPE column, T-> TTL pad, C-> CMOS pad

### 2 DETAILED SIGNAL DESCRIPTION

### 2.1 Processor Interface

| NAME         | GD610 | GD620  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SBHE*        | INPUT | INPUT  | Host CPU System Byte High Enable. This signal is sampled<br>only if the 16-bit mode is enabled (3C5 index C7:0), otherwise<br>8-bit bus operations are assumed. 16-bit mode is only for<br>video memory access. I/O port accesses are always 8-bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CPUADDR [18  | :16]  | INPUT  | The GD620 uses 3 upper address bits from the host CPU along with CPU-AD and CS for all decoding.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CPU-AD[15:0] | I/O   | I/O    | Bi-directional multiplexed address/data bus between the CPU and the chip set for video RAM addresses, I/O and switch data .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CS           |       | INPUT  | Memory Input, decoded from LA[23:19] for low 1Mbyte operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

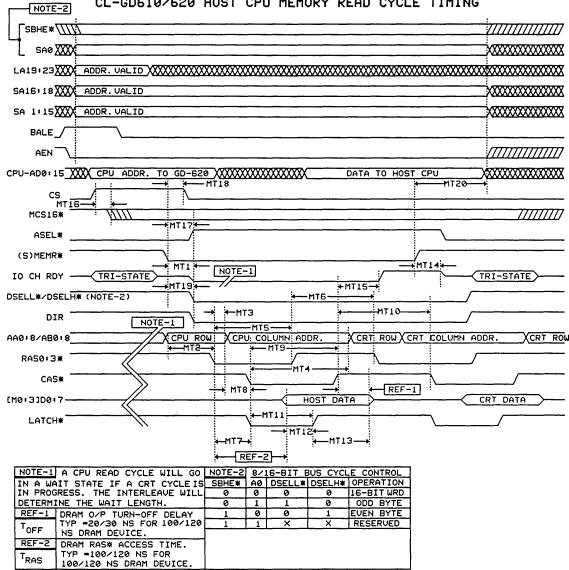

| CPURDY       |       | OUTPUT | This signal is inactive (tri-state) when no video memory<br>request is pending. The request may be either MEMR* or<br>MEMW*. At the beginning of a host CPU access to video<br>memory, CPURDY drops low, putting the host CPU in a<br>wait-state. This condition is held until the video memory<br>sequencer fits the memory request into the next available<br>"slot". At completion of the sequencers' host CPU memory<br>cycle, CPURDY is driven high until MEMR* and MEMW*<br>go inactive and then returns to the tri-state condition.                                                                                                                                                                                                                                                                                                                                               |

| CRTINT       |       | OUTPUT | This signal is enabled by clearing Bit 5 of the Vertical Retrace<br>End Register and cleared by resetting Bit 4 of the Vertical<br>Retrace End Register. When enabled, the CRTINT pin will go<br>high at the start of the vertical retrace interval and remain high<br>until cleared by a write of "0"to Bit 4 of the Vertical Retrace<br>End Register (CR11). CRTINT is enabled by:<br>•Clearing bit 5 of CR11<br>• Setting bit 4 of CR11<br>If bit 4 is not reset to a "1" after clearing the initial<br>CRTINT, interrupts will cease. The CR11 of the GD620 is<br>also readable. This feature simplifies greatly the task of ORing<br>in the proper value for the remaining bits of the CR11 register<br>(this is not the case for an IBM-EGA or VGA controller). This<br>Display Retrace Interrupt may be programmed for the AT Bus,<br>or a direct interrupt controller interface. |

| DIR/CARDSEL  | *     | OUTPUT | Controls the direction of the data flow on the bi-directional CPUDATA bus. Driven low when the CPU is performing an I/O or memory read cycle. This signal can also be used for PC XT slot-8 control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

### 2.1 Processor Interface (cont'd)

| NAME        | GD610 | GD620  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IORD*,IOWR* | INPUT | INPUT  | When low, these signals indicate that an IORD* or IOWR*cycle is taking place. The GD610/620 will respond only if CS is also active and the proper I/O port addresses have been decoded internally, and if not in the sleep mode.                                                                                                                                                                                                                                                                            |

| RESET       | INPUT | INPUT  | This input is normally connected to the system reset bus sig-<br>nal and is used as a hardware reset of the GD610/620 chips.<br>The GD620 may be partially reset via software by clearing<br>SR0-bit 0 or 1. The falling edge of RESET* latches the data<br>bus into switch registers to control S/W selectable functions.<br>Two pins, CPU-AD15,14 control H/W options at this time.                                                                                                                       |

| REFRESH*    |       | INPUT  | Indicates host system refresh of bus attached main memory<br>and tells GD620 to ignore memory addresses on the bus.                                                                                                                                                                                                                                                                                                                                                                                         |

| AEN         |       | INPUT  | Host CPU bus signal that distinguishes between DMA and<br>non-DMA bus cycles. The signal is high for a DMA cycle.                                                                                                                                                                                                                                                                                                                                                                                           |

| BALE        |       | INPUT  | Host CPU bus buffered address latch enable signal. High indicates a valid memory address.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MCS16*      |       | OUTPUT | This output is an acknowledge for 16-bit wide accesses and is<br>generated by the GD620 only if the 16-bit peripheral mode is<br>enabled and a valid memory address range has been decoded. It<br>may be generated by a full internal decode (LA16:23,<br>SA15:14), a partial internal decode (without SA15) or with<br>external decoding for fastest response time.                                                                                                                                        |

| MEMR*/W*    |       | INPUT  | Video memory read and write strobes. These inputs are driven<br>INPUT low on all CPU memory read/write accesses. Video<br>memory will be accessed if the GD610/620 chipset internal<br>address decoders determine that the partial decode of the MSB<br>addresses of the CPU address bus lies in the AxxxxH or<br>BxxxxH range. The GD610 chip is not connected to MEMW*<br>signal. It decodes this operation if a valid CPU cycle is in<br>progress, (CPUCYC*=0) and a read is not occurring<br>(MEMR*=1). |

### 2.2 Video Memory Interface

| NAME          | GD610 | GD620  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                               |

|---------------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AA [8:0]      |       | OUTPUT | Multiplexed video memory address bus A. This bus contains<br>the row/column address information required by the DRAMS<br>in the video memory for memory planes 0 and 1. The<br>GD610/620 chipset may be programmed to support 64Kx4 or<br>256Kx4 DRAMs (256KB or 1MB total video memory). This<br>bus carries different addresses than AB in text modes.  |

| AB [8:0]      |       | OUTPUT | Multiplexed video memory address bus B. This bus contains<br>the row/column address information required by the DRAMS<br>in the video memory for memory planes 2 and 3. The<br>GD610/620 chipset may be programmed to support 64Kx4 or<br>256Kx4 DRAMs (256KB or 1MB total video memory). This<br>bus carries different addresses than AA in text modes.  |

| CAS*          |       | OUTPUT | Video memory DRAM column address strobe. A low going<br>edge on this signal latches the column address (contained on<br>the AA and AB address busses) into video memory.                                                                                                                                                                                  |

| CGSEL         |       | INPUT  | Enabled by the sequencer character map select register, this bit<br>(normally connected to M1D3 of the attribute memory plane<br>in text mode) can be used to access 1 of 16 secondary character<br>sets (instead of the normal intensity function), to give a total<br>of 512 active display characters from a total of 4096.                            |

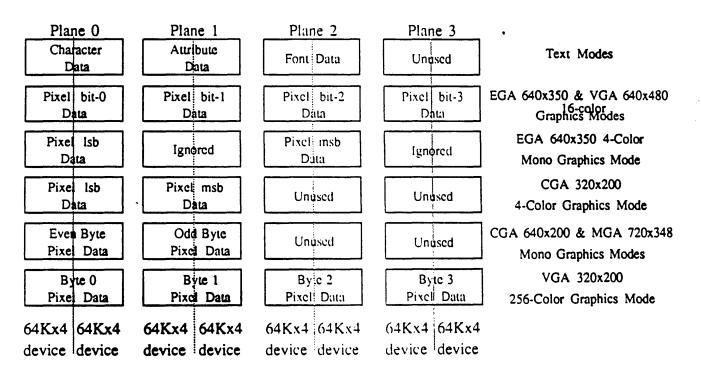

| M3D [7:0]     | I/O   |        | This bi-directional video memory data bus is controlled by the GD610 for read/write operations into video memory Plane 3 which stores graphic data for color plane #3, and eight extra alternate fonts in text modes.                                                                                                                                     |

| <br>M2D [7:0] | I/O   |        | This bi-directional video memory data bus is controlled by the GD610 for read/write operations into video memory Plane 2 which stores graphic data for color plane #2 or character generator font tables in the text modes.                                                                                                                               |

| M1D [7:0]     | I/O   | -      | Bi-directional video memory data bus controlled by GD610 for<br>read/write operations into video memory Plane 1 which stores<br>graphic data for color plane #1 or attribute codes in text modes.                                                                                                                                                         |

| M0D [7:0]     | I/O   | INPUT  | This bi-directional video memory data bus is controlled by the GD610 for read/write operations into video memory Plane 0 which stores graphic data for color plane #0 or attribute codes in the text modes. The GD620 uses these character codes in text mode to produce the proper address on the memory AB bus to access the character generator fonts. |

| RAS [3:0]*    |       | OUTPUT | Video memory DRAM row address strobes. A low going edge<br>on these signals latch the row address (contained on the AA<br>and AB address busses) into the video memory DRAMs.                                                                                                                                                                             |

| WE*           |       | OUTPUT | When low, this signal enables a video memory write to the bank selected by the appropriate RAS* signal(s). The actual write occurs on the falling edge of CAS*.                                                                                                                                                                                           |

### 2.3 Video Interface

The PIXEL DATA bits drive the analog or digital inputs of color or monochrome displays. When driving dual-line LCD panels, P4-P7 drive the upper panel data inputs, and P0-P3 drive the lower panel data inputs. P0-P7 pins are described more fully in the following table:

| NAME        | DESCR.                           | Analog<br>RAM DAC<br>Interface | ECD<br>64-Color<br>Digital | CD<br>16-Color<br>Digital | MD<br>Mono-<br>chrome | LCD | GD610           |

|-------------|----------------------------------|--------------------------------|----------------------------|---------------------------|-----------------------|-----|-----------------|

| P7 / FEAT1  | Tertiary Red<br>Feature Bit 1†   | P7                             | 0                          | 0                         | 0                     | UD3 | OUTPUT<br>INPUT |

| P6 / FEAT0  | Tertiary Green<br>Feature Bit 0† | P6                             | 0                          | 0                         | 0                     | UD2 | OUTPUT<br>INPUT |

| P5 / SR     | Secondary Red                    | P5                             | SR                         | Ι                         | Note                  | UD1 | OUTPUT          |

| P4 / SG / I | Secondary Green/<br>Intensity    | P4                             | SG                         | Ι                         | Note                  | UD0 | OUTPUT          |

| P3 / SB / V | Secondary Blue/<br>Video         | P3                             | SB                         | Ι                         | Note                  | LD3 | OUTPUT          |

| P2 / R      | Primary Red                      | P2                             | R                          | R                         | Note                  | LD2 | OUTPUT          |

| P1 / G      | Primary Green                    | P1                             | G                          | G                         | Note                  | LD1 | OUTPUT          |

| P0 / B      | Primary Blue                     | P0                             | В                          | В                         | Note                  | LD0 | OUTPUT          |

<sup>†</sup> FEAT1 and FEAT0 (Feature Bits 1 and 0) are programmable as inputs to the FC Register (Feature Control), and can be read at port address 3CA.

### Note:

In Monochrome modes, vidco outputs are driven from GD610 Palette Registers 0, 7, 8, 15 as follows:

| <u>Intensity</u> | <u>Video</u> | Palette Register<br>Selected | Mode                      |

|------------------|--------------|------------------------------|---------------------------|

| 0                | 0            | 0                            | Mono Text or HGC Graphics |

| 0                | 1            | 7                            | Mono Text or HGC Graphics |

| 1                | 0            | 8                            | Mono Text Only            |

| 1                | 1            | 15                           | Mono Text Only            |

Intensity = Text mode attribute byte bit 3

Video = Normal output to the monochrome display

| NAME | GD610  | GD620 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                          |

|------|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

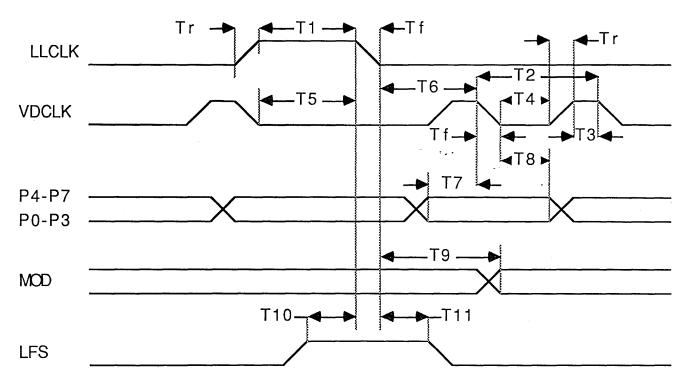

| MOD  | OUTPUT |       | Used to prevent DC polarization of LCD. MOD changes<br>polarity at least once per frame period. Some panels generate<br>randomized alternating signals derived from LLCLK to perform<br>this function, and may not need this signal. Its pulse width is<br>programmable. The period is twice the number of line clocks<br>written to register 3C5:D9 |

# $CL - GD \ 610/620$

### 2.3 Video Interface (cont'd)

| NAME  | GD610  | GD620   | DESCRIPTION                                                                                                                                                                                                                                                  |

|-------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LLCLK | OUTPUT |         | The LCD line clock is used to latch column segment data into<br>the horizontal shift registers. 4 bits of data for the upper panel,<br>and 4 bits of data for the lower panel are simultaneously<br>latched by this signal, for two corresponding scanlines. |

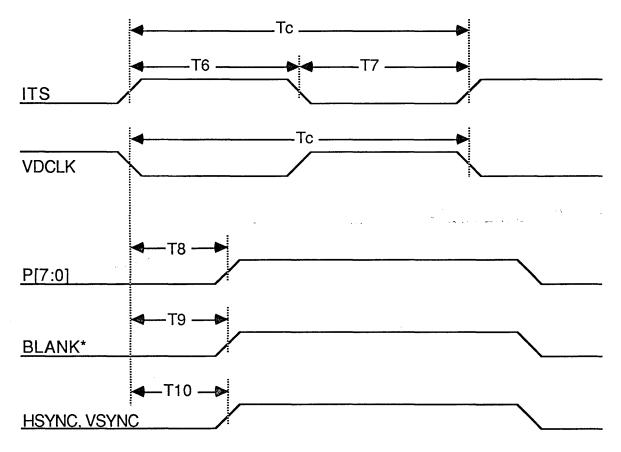

| VDCLK | OUTPUT |         | The Video clock is used to clock data through the horizontal<br>shift registers. This signal should be used for all video timing<br>purposes. It is used as a shift clock in LCD mode, and a pixel<br>clock in CRT modes.                                    |

| LFS   | OUTPUT | <u></u> | LCD Frame Start pulse that indicates the start of a new frame, resetting horizontal and vertical logic to the first nibble of the first (of top and bottom panel) scanline.                                                                                  |

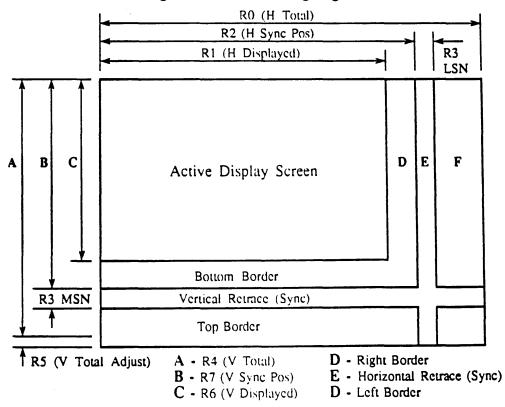

| HSYNC |        | OUTPUT  | Horizontal Sync. The active polarity of this signal can be se-<br>lected by bit 6 of the miscellaneous output register (I/O address<br>3C2hex) or bit 6 of the timing control register (extension ad-<br>dress 85H).                                         |

| VSYNC | INPUT  | OUTPUT  | Vertical Sync. The active polarity of this signal can be selected<br>by bit 7 of the miscellancous output register (I/O address<br>3C2H) or bit 7 of the timing control register (extension ad-<br>dress 85H).                                               |

### 2.4 External Interface

| NAME         | GD610 | GD620  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIOSA[15:13] |       | OUTPUT | These 3 pins select one of the five 8kbyte pages mapped into<br>the lower 8kbyte of the 32kbyte BIOS address space, allowing<br>a 64kbyte ROM to be used in this 32kbyte space.                                                                                                                                                                                                                                                                |

| OSC          |       | INPUT  | Oscillator input which MUST be connected to a clock, typically the 14.318 MHz clock from the system bus.                                                                                                                                                                                                                                                                                                                                       |

| CLK32,CLK28  | CLK25 | I/O    | These pins are configured as inputs or outputs based on the state of CPU-AD14 latched from the bus on the falling edge of RESET*. They may be driven from crystal oscillators to provide 32.514, 28.332, and 25.172 MHz inputs to the GD620's internal mux (a 16.257 MHz clock, when required, is internally generated). When configured as outputs, they provide select signals to an external PLL-based multi-frequency synthesizer circuit. |

| CKEXT        |       | I/O    | External clock input, typically from the feature connector, or used for LCD clock requirements.                                                                                                                                                                                                                                                                                                                                                |

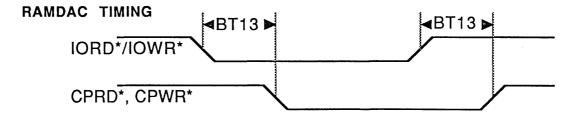

| CPWR*,CPRD   | *     |        | OUTPUT Color Palette write/read strobes. These pins are active when valid I/O reads or writes to port addresses xC6-xC9H are decoded.                                                                                                                                                                                                                                                                                                          |

# $CL - GD \ 610/620$

| <u>2.4</u> | <u>External_Int</u><br>NAME | <u>erface</u> (con<br>GD610 | t'd)<br>GD620 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|-----------------------------|-----------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | FC[1:0]                     | OUTPUT                      |               | General-purpose programmable output pins, normally used to<br>drive the feature connector. Can be used to enable/disable<br>battery-save modes for low-power laptop PC applications.<br>These bits may be write-protected with WRC bit 6.                                                                                                                                                                              |

|            | INTERNAL*                   |                             | OUTPUT        | Programmable output pin,normally driving tri-state control<br>pins of video drivers for internal or external (feature connec-<br>tor) video operation in CRT mode. This disables external<br>driver in LCD mode. MISC reg bit 4 controls this pin.                                                                                                                                                                     |

|            | BIOSEN*                     |                             | OUTPUT        | This signal is typically connected to a ROM BIOS's OE*<br>input. It enables the BIOS ROM's outputs if a memory<br>address in the C0000H-CFFFFH range has been decoded and<br>ROM control register bit 7 is cleared. This pin will not<br>activate if the BIOS resides on the 'CPU' side of the<br>address/data muxes as indicated by a low state of CPU-AD15<br>latched from the bus during the falling edge of RESET. |

|            | ASEL*,DSEL                  | H*,DSELL*                   | OUTPUT        | Address and data select (high and low byte) enables.                                                                                                                                                                                                                                                                                                                                                                   |

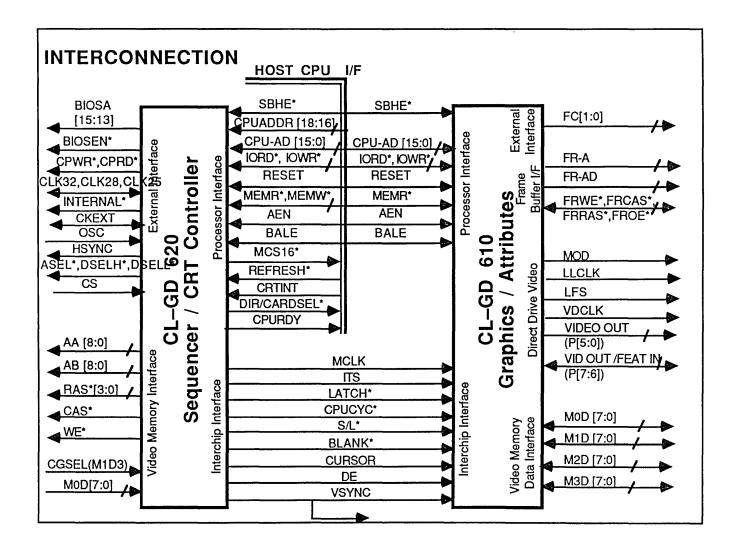

### 2.5 CL-GD610 / 620 Interconnect Signals

| NAME       | GD610 | GD620  | DESCRIPTION                                                                                                                                                                                                        |  |  |  |  |

|------------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

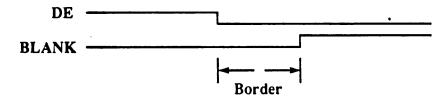

| BLANK* /DE | INPUT | OUTPUT | CRT Video Blanking signal and Display Enable signal. These signals function as follows:                                                                                                                            |  |  |  |  |

|            |       |        | LCD CRT CRT/LCD                                                                                                                                                                                                    |  |  |  |  |

|            |       |        | BLANK* BLANK* DE FUNCTION                                                                                                                                                                                          |  |  |  |  |

|            |       |        | dont care 0 – OFF (Screen is black)                                                                                                                                                                                |  |  |  |  |

|            |       |        | dont care 1 0 Border display                                                                                                                                                                                       |  |  |  |  |

|            |       |        | dont care 1 1 Active Screen                                                                                                                                                                                        |  |  |  |  |

|            |       |        |                                                                                                                                                                                                                    |  |  |  |  |

| CPUCYC*    | INPUT | OUTPUT | Active low during an actual CPU Video RAM read or write cycles. This signal brackets the LATCH* signal during a read operation. The GD610 also uses this signal to differentiate between CPU and CRT write cycles. |  |  |  |  |

| CURSOR*    | INPUT | OUTPUT | Active during valid cursor position.                                                                                                                                                                               |  |  |  |  |

| ITS        | INPUT | OUTPUT | Interchip Timing Strobe. This signal is in a critical timing path. Loading on this pin and the S/L* pin must be the same.                                                                                          |  |  |  |  |

| MCLK       | INPUT | OUTPUT | Derived from the currently selected clock, this is the master clock used to produce all of the signals in the GD610/GD620.                                                                                         |  |  |  |  |

| LATCH*     | INPUT | OUTPUT | Latches data to and from the video RAM in the GD610.                                                                                                                                                               |  |  |  |  |

| S/L*       | INPUT | OUTPUT | Shift / Load. Synchronizes the loading of the shift registers in the GD610. This signal is in a critical timing path. Loading on this pin and the ITS pin must be the same.                                        |  |  |  |  |

| VSYNC      | INPUT | OUTPUT | See description under video interface.                                                                                                                                                                             |  |  |  |  |

| NAME       | GD610  | GD620 | DESCRIPTION                             |  |

|------------|--------|-------|-----------------------------------------|--|

| FR-A[7:4]  | OUTPUT |       | Upper four bits of frame buffer address |  |

| FR-AD[3:0] | I/O    |       | Multiplexed frame buffer address/data   |  |

| FRWE*      | OUTPUT |       | Buffer write enable                     |  |

| FROE*      | OUTPUT |       | Buffer output enable                    |  |

| FRCAS*     | OUTPUT |       | Buffer CAS*                             |  |

| FRRAS*     | OUTPUT |       | Buffer RAS*                             |  |

### 2.6 LCD Display Frame Buffer Interface Signals

### 3 FUNCTIONAL DESCRIPTION

### 3.1 Functional Operation

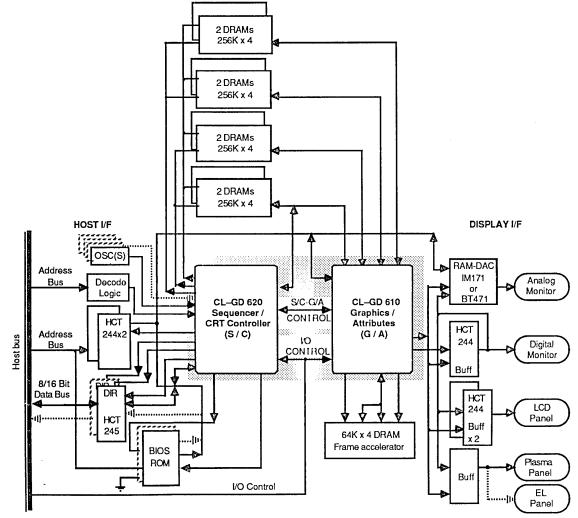

The CIRRUS LOGIC GD610 Graphics/ Attributes chip and CIRRUS LOGIC GD620 Sequencer/CRT Controller chip are tightly coupled and interface with the host processor, video memory, the display device and other external I/O.

The host interface may be 8 or 16 bits wide, under program control. Register LCDCNTL3 is provided to switch bus sizes.

Video memory may be 256Kbytcs or 1Mbyte of DRAM.

The display device is typically a 640 by 400/480 line LCD (or other flat panel type) but all standard TTL and analog CRT monitors are supported as well.

The four major operations supported by the CL-GD610/620 are:

- Host access to CL-GD610/620 registers

- Host access to video memory

- Memory refresh

- Display access to video memory

### Host Access to Registers

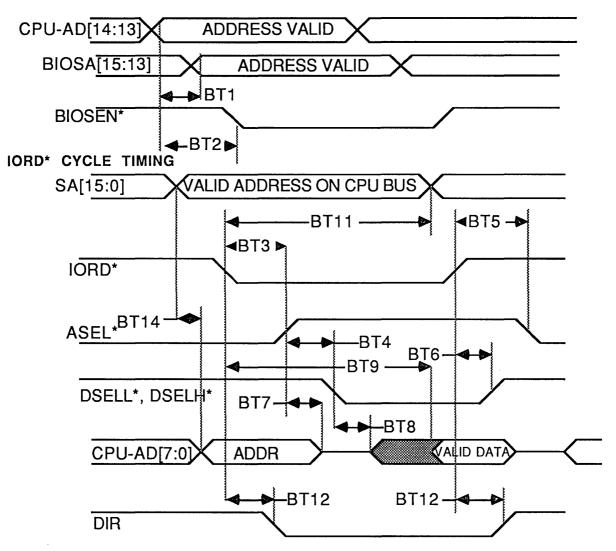

The host (typically an 8088/80286/80386 processor in an IBM PC/XT/AT bus compatible environment) can access CL-GD610/620 registers by setting up 24 bit addresses and generating IOR\* / IOW\* / MEMR\* / MEMW\* signals to read or write 8-bit or 16-bit data.

DRAM and screen refresh activities occur concurrently and independently (unless display parameters are being changed by the host CPU's actions on CL-GD610/620 registers).

The registers that may be accessed by the host are listed in sections 4 and 5. They include the registers of the IBM VGA, EGA, CGA, MDA, and Hercules HGC, including those of the 6845 CRT controller. Non-VGA registers have also been made host-readable and writable in order to allow BIOS and driver software to determine the state of the graphics adapter. The state may thus be readily switched and restored in multi-tasking and windowing environments. These so-called extension registers provide the numerous enhancements to the basic VGA function listed in the features/benefits section.

Host access to video memory is channelled via the CL-GD610/620. The host must set up the proper address/data/timing parameters in CL-GD610/620 registers, then handshake with the CL-GD610/620 in order to connect the host data bus to one of the 4 video memory byte plane buses. For example, consider VGA/EGA operation:

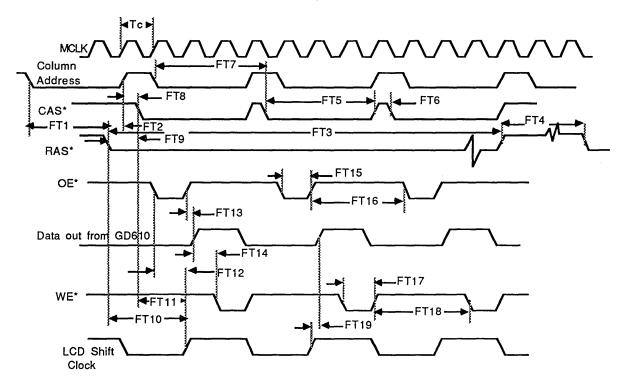

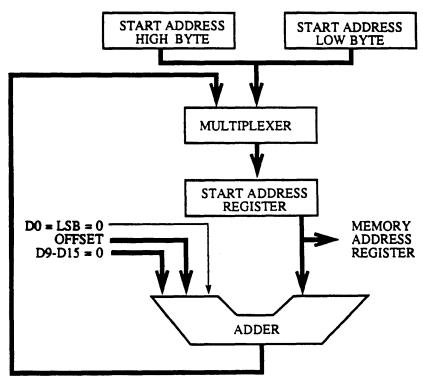

Byte planes 0 and 1 share address bus A; planes 2 and 3 share the address bus B. The GD620 Sequencer/CRT Controller chip takes 17-bit addresses from the host, and transforms them according to the selected addressing mode and address space mappings, finally issuing multiplexed addresses to the different planes via the A and B address buses. The CAS\* signal, four RAS\* signals, and WE\* are also generated.

Note that the GD620 Sequencer/CRT Controller chip also contains an intelligent address sequencer that allocates video memory cycles not only to the host, as just described, but also to the DRAM refresh controller and the display CRT controller.

### **Memory Refresh**

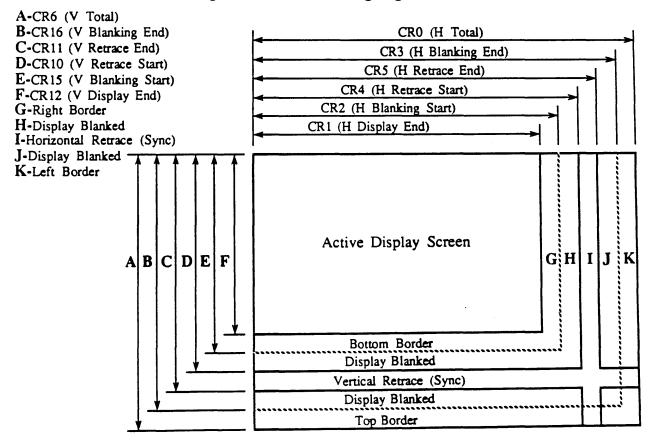

Memory bandwidth is allocated to each process according to the actual realtime needs of the process, ensuring efficient use of the available bandwidth. In the case of a CRT display device, the display is blanked during horizontal and vertical retrace intervals, freeing up memory bandwidth for host access and/or memory refresh.

The CL-GD610/620, unlike early VGA implementations that gave the host only 14% of memory cycles, can give the host from 25-50% access to video memory (1 out of 2 memory cycles), largely due to the sequencing strategy.

### **Display Access to Video Memory**

The GD620 Sequencer/CRT Controller chip works very closely with the GD610 Graphics/Attributes chip in all video modes, as the GD610 actually contains the video memory data interface as well as the video outputs to the display device. Thus the display data is latched in the GD610 after the GD620 determines where it is. Note that due to the 32-bit memory data interface, character data and attribute data can be pipelined. The GD610 contains the video shift registers to interface to the display device. The GD620 works with the GD610 in order to fetch scan line data from the font bitmaps, separately controlling the A and B address buses.

Foreground and background attributes are specified for each character in alphanumeric mode. Cursors and borders are also controlled by the GD610 in alpha modes.

In bit-mapped graphics (All Points Addressable) modes, pixel data is latched into the GD610 Graphics/Attributes chip, transferred to shift registers, and shifted out upon translation through the color palette registers, which are also contained in the GD610.

The GD620 Sequencer/CRT Controller chip supplies a clock (ITS) to the GD610 Graphics/Attributes chip, as well as display memory read strobe (LATCH\*), CPU read/ write cycle (CPUCYC\*), and shift register load (S/L\*).

The GD620 Sequencer/CRT Controller chip keeps track of the active and unused areas of the screen and cursor positions and consequently supplies screen control signals (VSYNC, BLANK, Display Enable DE, and CURSOR) to the GD610 Graphics/ Attributes chip.

When the GD610/620 are interfaced to an LCD display, an additional 64Kx4 DRAM is needed. This device is used by the chipset to accelerate panel refresh without using high-frequency clocks, thus reducing power, and, allowing vertical refresh rates from 60Hz to 160Hz for improved contrast and freedom from flicker.

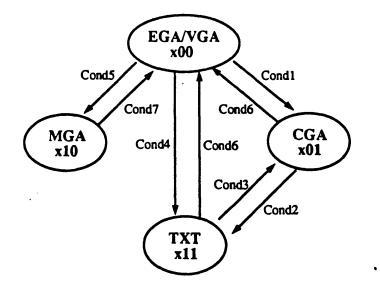

### 3.2 CRT Display Compatibility Modes

The CL-GD610/620 includes all registers and data paths required for VGA/EGA, CGA, MDA, and HGC controllers. VGA enhancements to baseline EGA functionality include 320x200 eight-bit/pixel mode and support for an external color palette, 16 (double IBM's

capability) simultaneously loadable text fonts, write mode 3, and readable registers.

These devices provide support for new extended resolution display modes with CRT displays.

Extended graphics resolutions beyond the 640x480 IBM VGA standard are available using either multiple frequency monitors such as the NEC MultiSync<sup>™</sup> or Sony MultiScan<sup>™</sup> \ or single frequency PS/2 monitors such as the IBM 8514. These include a 720 x 540 mode which has a 4:3 aspect ratio (square pixels on typical monitors). This mode is supported on both PS/2 monitors as well as multifrequency displays. In addition there is an 800 x 600 mode which has a 4:3 aspect ratio (the same as 640 x 480 and 720 x 540). This mode requires a multi-frequency display. There are also high resolution text modes from 100 columns by 30 rows up to 132 columns by 60 rows.

Additional 256 color modes (besides IBM mode 13) are available in the chipset and the Cirrus Logic BIOS supports these as well.

The chip set also supports an extended mode 13 where 4 (256Kb RAM) or 16 (1Mb RAM) pages of 64K blocks of memory can be switched and displayed instead of the IBM VGA's single page. This will allow for animation using 256 displayable colors without requiring a large amount of data to be manipulated (64K maximum size per image).

### 3.3 Flat Panel Display Compatibility Modes

The GD610/620 chip set will directly drive all of the popular dual panel/dual scan flat panels from manufacturers such as Sharp, Hitachi, Sanyo, Epson, Kyocera, Optrex, Toshiba etc

Proprietary techniques minimize flicker, noise and pattern motion while enhancing contrast within the gray scales being used.

Gray-scaling is accomplished by modulating the ON to OFF time of individual pixels in the panel and allowing the eye to integrate the superposed pixels to 16 perceptible gray scales. Flicker is eliminated by proprietary techniques involving distribution of time between ON and OFF pixels during frame modulation.

# $CL - GD \ 610/620$

The GD610/620 provides various mechanisms in order to allow the full spectrum of PC applications, written for various TTL and analog monitors, and various video modes, to run on standard 640x400 and 640x480 flat panels.

These mechanisms include color emulation, attribute remapping, resolution mapping, etc

In addition, summing circuitry allows rapid generation of IBM-compatible gray-scale equivalents of color images. Up to 32 gray scales are available using algorithms similar to those used with IBM PS/2-monochrome CRT monitors, enhanced with Cirrus Logicproprietary 2-dimensional stippling logic. This allows running all applications generating monochrome, 4, 16, or 256 color images with a monochrome flat panel display. CIRRUS LOGIC's AutoMap<sup>TM</sup> logic is capable of mapping 256 colors to a stunning monochrome image appearing in 32 gray scales. The hardware-based algorithm maintains independence of the particular palette map being used by calculating and storing (in real time) 5 bit gray scale values in an internal palette RAM that reflects all writes to the external RAMDAC. RAMDAC data may be stored as desired by the application in orderly sequences or in random sequences without affecting the consistently realistic renditions of color images.

In color text modes, foreground and background attributes can be automatically remapped to black and white for maximum contrast. Positive or negative raster may be selected under program control to match the visual qualities of the display and/or needs of the application. Bold characters are generated by using built-in intensified text fonts when the attribute calls for intensification.

The video resolutions that an application has selected are remapped to a flat panel according to whether compatibility mode, compression mode or expanded mode was selected.

In compatible text mode, the image is centered on the display with no change in the number of scanlines (200 line modes are double scanned to 400, however). 9 dot character fonts are replaced by 8 dot character fonts (HGC and VGA text) in order to fit within 640 columns. If alternate fonts from plane 3 are used, 9-dot fonts are no longer available. In compatible graphics mode, the image is centered on the screen, with no change to the number of pixels displayed (except for double scanning 200 line CGA graphics modes). HGC images are 720x348, so panning with a 640 pixel wide window may be performed to view the entire image.

Compression mode allows the 720 horizontal pixels of an HGC generated image to be displayed on a 640 pixel-wide display. Under program control, the 8th and 9th bit of each 9bit word may be AND'ed or suppressed to generate the compressed bit. This compression provides very little degradation to text, and panning is always available if compressed graphics do not look satisfactory.

Expansion mode lets the display be filled in a symmetric and ratiometrically determined fashion and is available for both text and graphics video modes. In text modes, 9-dot characters are replaced by 8-dot characters, and character cell heights are expanded (from 8, 14, or 16 scanlines) to 19 scanlines. Thus 25 text-lines become 475 scanlines filling most of a 480 scanline panel. The filling algorithm was designed for a symmetric, pleasing expansion of the text, and automatically extends pixels used in character-based graphics applications to the cell boundaries.

Laptop PCs have stringent power dissipation limits. The GD610/620 chip set supports these objectives by being fabricated in lowpower CMOS, and by having the ability to drop down to a low-power mode. In this lowpower mode, the clock to the GD610 is stopped, and the clock to the RAMDAC is stopped. Low-power static or pseudo-static RAM may also be used in the system.

The FC bits may be used to control power to devices such as the RAMDAC, LCD back-panel, and other H/W.

Low total system component count also contributes to minimizing power consumption. This low chip count is achieved by eliminating most glue logic. For example, an add-in card with an 8-bit host interface can be designed with 16 ICs or less; one with a 16-bit I/F would need no more than 21 ICs.

### 3.4 Supported Screen Formats

PS/2 (Single Frequency Analog Display, IBM 85xx series-compatible)

|            |          |        |       |          |          | s-compannie |               | ~~ <b>~</b>    | <b>.</b> . |

|------------|----------|--------|-------|----------|----------|-------------|---------------|----------------|------------|

|            | No. of   | Char.  | Char. | Video    | Display  | Screen      | Buffer        | CRT            | Dot        |

| <u>No.</u> | Colors   | x Row  | Cell  | Mode     | Mode     | Format      | Start         | H/V Sync.      | Clock      |

| 0          | 4/256K   | 40x25  | 8x8   | CGA      | Text     | 320x200     | B8000         | 31.5KHz/70Hz   | 25.172MHz  |

| 0*         | 16/256K  | 40x25  | 8x14  | EGA      | Text     | 320x350     | B8000         | 31.5KHz/70Hz   | 25.172MHz  |

| 0/1+       | 16/256K  | 40x25  | 9x16  | VGA      | Text     | 360x400     | B8000         | 31.5KHz/70Hz   | 28.332MHz  |

| 1          | 4/256K   | 40x25  | 8x8   | CGA      | Text     | 320x200     | B8000         | 31.5KHz/70Hz   | 25.172MHz  |

| 1*         | 16/256K  | 40x25  | 8x14  | EGA      | Text     | 320x350     | B8000         | 31.5KHz/70Hz   | 25.172MHz  |

| 2          | 4/256K   | 80x25  | 8x8   | CGA      | Text     | 640x200     | B8000         | 31.5KHz/70Hz   | 25.172MHz  |

| 2*         | 16/256K  | 80x25  | 8x14  | EGA      | Text     | 640x350     | B8000         | 31.5KHz/70Hz   | 25.172MHz  |

| 2/3+       | 16/256K  | 80x25  | 9x16  | VGA      | Text     | 720x400     | B8000         | 31.5KHZ/70Hz   | 28.332MHZ  |